## Complete 12-Bit 10 MSPS Monolithic A/D Converter

## AD872A

#### FEATURES

Monolithic 12-Bit 10 MSPS A/D Converter Low Noise: 0.26 LSB RMS Referred-to-Input No Missing Codes Guaranteed Differential Nonlinearity Error: 0.5 LSB Signal-to-Noise and Distortion Ratio: 68 dB Spurious-Free Dynamic Range: 75 dB Power Dissipation: 1.03 W Complete: On-Chip Track-and-Hold Amplifier and Voltage Reference Twos Complement Binary Output Data Out-of-Range Indicator 28-Lead Ceramic DIP or 44-Terminal Leadless Chip Carrier Package

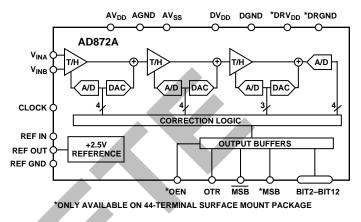

#### FUNCTIONAL BLOCK DIAGRAM

#### **PRODUCT DESCRIPTION**

The AD872A is a monolithic 12-bit, 10 MSPS analog-to-digital converter with an on-chip, high performance track-and-hold amplifier and voltage reference. The AD872A uses a multistage differential pipelined architecture with error correction logic to provide 12-bit accuracy at 10 MSPS data rates and guarantees no missing codes over the full operating temperature range. The AD872A is a redesigned version of the AD872 which has been optimized for lower noise. The AD872A is pin compatible with the AD872, allowing the parts to be used interchangeably as system requirements change.

The low noise input track-and-hold (T/H) of the AD872A is ideally suited for high-end imaging applications. In addition, the T/H's high input impedance and fast settling characteristics allow the AD872A to easily interface with multiplexed systems that switch multiple signals through a single A/D converter. The dynamic performance of the T/H also renders the AD872A suitable for sampling single channel inputs at frequencies up to and beyond the Nyquist rate. The AD872A provides both reference output and reference input pins, allowing the onboard reference to serve as a system reference. An external reference can also be chosen to suit the dc accuracy and temperature drift requirements of the application. A single clock input is used to control all internal conversion cycles. The digital output data is presented in twos complement binary output format. An out-ofrange signal indicates an overflow condition, and can be used with the most significant bit to determine low or high overflow.

The AD872A is fabricated on Analog Devices' ABCMOS-l process that utilizes high speed bipolar and CMOS transistors on a single chip.

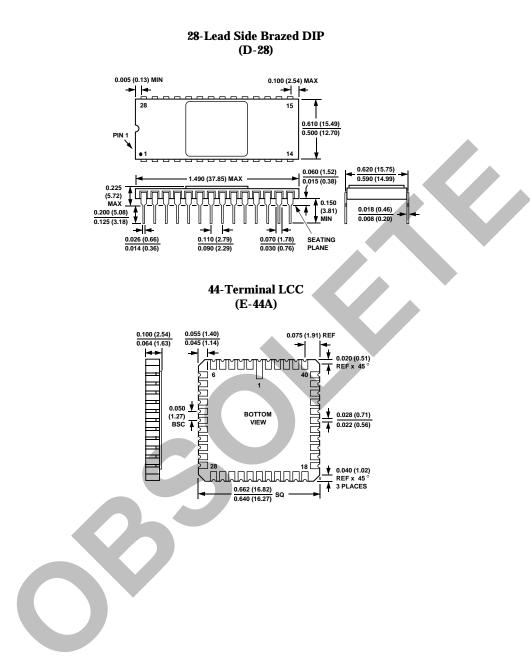

The AD872A is packaged in a 28-lead ceramic DIP and a 44terminal leadless ceramic surface mount package (LCC). Operation is specified from  $0^{\circ}$ C to  $+70^{\circ}$ C and  $-55^{\circ}$ C to  $+125^{\circ}$ C.

#### **PRODUCT HIGHLIGHTS**

The AD872A offers a complete single-chip sampling, 12-bit 10 MSPS analog-to-digital conversion function in a 28-lead DIP or 44-terminal LCC.

*Low Noise*—The AD872A features 0.26 LSB rms referred to-input noise.

*Low Power*—The AD872A at 1.03 W consumes a fraction of the power of presently available hybrids.

*On-Chip Track-and-Hold (T/H)*—The low noise, high impedance T/H input eliminates the need for external buffers and can be configured for single-ended or differential inputs.

*Ease of Use*—The AD872A is complete with T/H and voltage reference and is pin-compatible with the AD872.

*Out of Range* (OTR)—The OTR output bit indicates when the input signal is beyond the AD872A's input range.

#### REV. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

# AD872A-SPECIFICATIONS

**DC SPECIFICATIONS** ( $T_{MIN}$  to  $T_{MAX}$ ,  $AV_{DD} = +5$  V,  $DV_{DD} = +5$  V,  $AV_{SS} = -5$  V,  $f_{SAMPLE} = 10$  MHz unless otherwise noted)

| Parameter                                                                                                                                                                        | J Grade <sup>1</sup>                                 | S Grade <sup>1</sup>                                 | Units                                                                                                                                                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESOLUTION                                                                                                                                                                       | 12                                                   | 12                                                   | Bits min                                                                                                                                              |

| MAX CONVERSION RATE                                                                                                                                                              | 10                                                   | 10                                                   | MHz min                                                                                                                                               |

| INPUT REFERRED NOISE                                                                                                                                                             | 0.26                                                 | 0.26                                                 | LSB rms typ                                                                                                                                           |

| ACCURACY<br>Integral Nonlinearity (INL)<br>Differential Nonlinearity (DNL)<br>No Missing Codes<br>Zero Error (@ +25°C) <sup>2</sup><br>Gain Error (@ +25°C) <sup>2</sup>         | ${}^{\pm 1.75}_{\pm 0.5}_{12}_{\pm 0.75}_{\pm 1.25}$ | ${}^{\pm 1.75}_{\pm 0.5}_{12}_{\pm 0.75}_{\pm 1.25}$ | LSB typ<br>LSB typ<br>Bits Guaranteed<br>% FSR max<br>% FSR max                                                                                       |

| TEMPERATURE DRIFT<br>Zero Error<br>Gain Error <sup>3, 4</sup><br>Gain Error <sup>3, 5</sup>                                                                                      | $\pm 0.15 \\ \pm 0.80 \\ \pm 0.25$                   | ${\scriptstyle \pm 0.3 \ \pm 1.75 \ \pm 0.50}$       | % FSR max<br>% FSR max<br>% FSR max                                                                                                                   |

| POWER SUPPLY REJECTION <sup>6</sup><br>AV <sub>DD</sub> , DV <sub>DD</sub> (+5 V $\pm$ 0.25 V)<br>AV <sub>SS</sub> (-5 V $\pm$ 0.25 V)                                           | $\pm 0.125 \\ \pm 0.125$                             | $\pm 0.125 \\ \pm 0.125$                             | % FSR max<br>% FSR max                                                                                                                                |

| ANALOG INPUT<br>Input Range<br>Input Resistance<br>Input Capacitance                                                                                                             |                                                      | $     \pm 1.0     50     10 $                        | V max<br>kΩ typ<br>pF typ                                                                                                                             |

| INTERNAL VOLTAGE REFERENCE<br>Output Voltage<br>Output Voltage Tolerance<br>Output Current (Available for External Loads)<br>(External Load Should Not Change During Conversion) | 2.5<br>±20<br>2.0                                    | $2.5 \pm 40 \\ 2.0$                                  | V typ<br>mV max<br>mA typ                                                                                                                             |

| REFERENCE INPUT RESISTANCE                                                                                                                                                       | 5                                                    | 5                                                    | kΩ                                                                                                                                                    |

| POWER SUPPLIES<br>Supply Voltages<br>AV <sub>DD</sub><br>AV <sub>SS</sub><br>DV <sub>DD</sub><br>DRV <sub>DD</sub> <sup>7</sup><br>Supply Current                                | +5<br>-5<br>+5<br>+5                                 | +5<br>-5<br>+5<br>+5                                 | V (±5% AV <sub>DD</sub> Operating)<br>V (±5% AV <sub>SS</sub> Operating)<br>V (±5% DV <sub>DD</sub> Operating)<br>V (±5% DRV <sub>DD</sub> Operating) |

| IAV <sub>DD</sub><br>IAV <sub>SS</sub><br>IDV <sub>DD</sub><br>IDRV <sub>DD</sub> <sup>7</sup>                                                                                   | 91<br>147<br>20<br>2                                 | 92<br>150<br>21<br>2                                 | mA max (85 mA typ)<br>mA max (115 mA typ)<br>mA max (7 mA typ)<br>mA                                                                                  |

| POWER CONSUMPTION                                                                                                                                                                | 1.03<br>1.25                                         | 1.03<br>1.3                                          | W typ<br>W max                                                                                                                                        |

NOTES

<sup>1</sup>Temperature ranges are as follows: J Grade:  $0^{\circ}$ C to  $+70^{\circ}$ C, S Grade:  $-55^{\circ}$ C to  $+125^{\circ}$ C.

<sup>2</sup>Adjustable to zero with external potentiometers (see Zero and Gain Error Calibration section).

<sup>3</sup>+25°C to T<sub>MIN</sub> and +25°C to T<sub>MAX</sub>.

<sup>4</sup>Includes internal voltage reference drift.

<sup>5</sup>Excludes internal voltage reference drift.

<sup>6</sup>Change in Gain Error as a function of the dc supply voltage (V<sub>NOMINAL</sub> to V<sub>MIN</sub>, V<sub>NOMINAL</sub> to V<sub>MAX</sub>).

<sup>7</sup>LCC package only.

Specifications subject to change without notice.

AC SPECIFICATIONS ( $T_{MIN}$  to  $T_{MAX}$ ,  $AV_{DD} = +5 V$ ,  $DV_{DD} = +5 V$ ,  $AV_{SS} = -5 V$ ,  $f_{SAMPLE} = 10 \text{ MHz}$  unless otherwise noted)<sup>1</sup>

| Parameter                                     | J Grade | S Grade | Units      |

|-----------------------------------------------|---------|---------|------------|

| SIGNAL-TO-NOISE & DISTORTION RATIO (S/N+D)    |         |         |            |

| $f_{INPUT} = l MHz$                           | 68      | 68      | dB typ     |

|                                               | 61      | 61      | dB min     |

| $f_{INPUT} = 4.99 \text{ MHz}$                | 66      | 66      | dB typ     |

| SIGNAL-TO-NOISE RATIO (SNR)                   |         |         |            |

| $f_{INPUT} = 1 \text{ MHz}$                   | 69      | 69      | dB typ     |

| $f_{INPUT} = 4.99 \text{ MHz}$                | 67      | 67      | dB typ     |

| TOTAL HARMONIC DISTORTION (THD)               |         |         |            |

| $f_{\text{INPLIT}} = 1 \text{ MHz}$           | -74     | -74     | dB typ     |

| INOT                                          | -63     | -62     | dB max     |

| $f_{INPUT} = 4.99 \text{ MHz}$                | -72     | -72     | dB typ     |

| SPURIOUS-FREE DYNAMIC RANGE (SFDR)            |         |         |            |

| $f_{\text{INPUT}} = 1 \text{ MHz}$            | 75      | 75      | dB typ     |

| $f_{INPUT} = 4.99 \text{ MHz}$                | 74      | 74      | dB typ     |

| INTERMODULATION DISTORTION (IMD) <sup>2</sup> |         |         |            |

| Second Order Products                         | -80     | -80     | dB typ     |

| Third Order Products                          | -73     | -73     | dB typ     |

|                                               |         |         |            |

| FULL POWER BANDWIDTH                          | 35      | 35      | MHz typ    |

| SMALL SIGNAL BANDWIDTH                        | 35      | 35      | MHz typ    |

| APERTURE DELAY                                | 6       | 6       | ns typ     |

| APERTURE JITTER                               | 16      | 16      | ps rms typ |

| ACQUISITION TO FULL-SCALE STEP                | 40      | 40      | ns typ     |

| OVERVOLTAGE RECOVERY TIME                     | 40      | 40      | ns typ     |

|                                               |         | •       | 1          |

NOTES

${}^{1}f_{INPUT}$  amplitude = -0.5 dB full scale unless otherwise indicated. All measurements referred to a 0 dB (1.0 V pk) input signal unless otherwise indicated.  ${}^{2}f_{a} = 1.0 \text{ MHz}$ , fb = 0.95 MHz with t<sub>SAMPLE</sub> = 10 MHz.

Specifications subject to change without notice.

### **DIGITAL SPECIFICATIONS** (T<sub>MIN</sub> to T<sub>MAX</sub>, $AV_{DD} = +5 V$ , $DV_{DD} = +5 V$ , $AV_{SS} = -5 V$ , $f_{SAMPLE} = 10 MHz$ unless otherwise noted)

| Parameter                                               | Symbol          | J, S Grades | Units  |

|---------------------------------------------------------|-----------------|-------------|--------|

| LOGIC INPUTS                                            |                 |             |        |

| High Level Input Voltage                                | V <sub>IH</sub> | +2.0        | V min  |

| Low Level Input Voltage                                 | V <sub>IL</sub> | +0.8        | V max  |

| High Level Input Current ( $V_{IN} = DV_{DD}$ )         | I <sub>IH</sub> | 115         | μA max |

| Low Level Input Current $(V_{IN} = 0 V)$                | I <sub>IL</sub> | 115         | μA max |

| Input Capacitance                                       | Č <sub>IN</sub> | 5           | pF typ |

| LOGIC OUTPUT                                            |                 |             |        |

| High Level Output Voltage ( $I_{OH} = 0.5 \text{ mA}$ ) | V <sub>OH</sub> | +2.4        | V min  |

| Low Level Output Voltage ( $I_{OL} = 1.6 \text{ mA}$ )  | V <sub>OL</sub> | +0.4        | V max  |

| Output Capacitance                                      | $C_{OUT}$       | 5           | pF typ |

| Leakage (Three State, LCC Only)                         | IZ              | ±10         | μA max |

Specifications subject to change without notice.

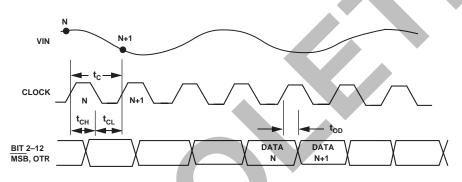

## $\label{eq:switching} \textbf{SWITCHING SPECIFICATIONS} \begin{array}{l} (T_{\text{MIN}} \text{ to } T_{\text{MAX}} \text{ with } \text{AV}_{\text{DD}} = +5 \text{ V}, \text{ } \text{DV}_{\text{DD}} = +5 \text{ V}, \text{ } \text{DRV}_{\text{DD}} = +5 \text{ V}, \text{ } \text{AV}_{\text{SS}} = -5 \text{ V}; \text{ } \text{V}_{\text{IL}} = 0.8 \text{ V}, \\ v_{\text{IN}} = 2.0 \text{ V}, \text{ } v_{\text{OL}} = 0.4 \text{ V} \text{ and } v_{\text{OH}} = 2.4 \text{ V}) \end{array}$

| Parameter                                          | Symbol          | J, S Grades | Units                |

|----------------------------------------------------|-----------------|-------------|----------------------|

| Clock Period <sup>1</sup>                          | t <sub>C</sub>  | 100         | ns min               |

| CLOCK Pulsewidth High                              | t <sub>CH</sub> | 45          | ns min               |

| CLOCK Pulsewidth Low                               | t <sub>CL</sub> | 45          | ns min               |

| Clock Duty Cycle <sup>2</sup>                      |                 | 40          | % min (50% typ)      |

|                                                    |                 | 60          | % max                |

| Output Delay                                       | t <sub>OD</sub> | 10          | ns min (20 ns typ)   |

| Pipeline Delay (Latency)                           |                 | 3           | Clock Cycles         |

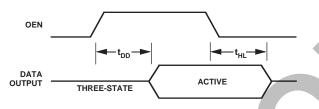

| Data Access Time (LCC Package Only) <sup>2</sup>   | t <sub>DD</sub> | 50          | ns typ (100 pF Load) |

| Output Float Delay (LCC Package Only) <sup>2</sup> | t <sub>HL</sub> | 50          | ns typ (10 pF Load)  |

#### NOTES

<sup>1</sup>Conversion rate is operational down to 10 kHz without degradation in specified performance. <sup>2</sup>See section on Three-State Outputs for timing diagrams and applications information.

Specifications subject to change without notice.

#### Figure 1. Timing Diagram

#### ABSOLUTE MAXIMUM RATINGS<sup>1</sup>

| ADSOLUTE MAXIMUM RATINGS                          |                          |                  |                  |       |

|---------------------------------------------------|--------------------------|------------------|------------------|-------|

| Parameter                                         | With Respect to          | Min              | Max              | Units |

| AV <sub>DD</sub>                                  | AGND                     | -0.5             | +6.5             | Volts |

| AV <sub>SS</sub>                                  | AGND                     | -6.5             | +0.5             | Volts |

| DV <sub>DD</sub> , DRV <sub>DD</sub> <sup>2</sup> | DGND, DRGND <sup>2</sup> | -0.5             | +6.5             | Volts |

| DRV <sub>DD</sub> <sup>2</sup>                    | DV <sub>DD</sub>         | -6.5             | +6.5             | Volts |

| DRGND                                             | DGND                     | -0.3             | +0.3             | Volts |

| AGND                                              | DGND                     | -1.0             | +1.0             | Volts |

| AV <sub>DD</sub>                                  | DV <sub>DD</sub>         | -6.5             | +6.5             | Volts |

| Clock Input, OEN <sup>2</sup>                     | DGND                     | -0.5             | $DV_{DD} + 0.5$  | Volts |

| Digital Outputs                                   | DGND                     | -0.5             | $DV_{DD} + 0.3$  | Volts |

| V <sub>INA</sub> , V <sub>INB</sub> , REF IN      | AGND                     | -6.5             | +6.5             | Volts |

| REF IN                                            | AGND                     | AV <sub>SS</sub> | AV <sub>DD</sub> | Volts |

| Junction Temperature                              |                          |                  | +150             | °C    |

| Storage Temperature                               |                          | -65              | +150             | °C    |

| Lead Temperature (10 sec)                         |                          |                  | +300             | °C    |

| -                                                 |                          |                  |                  |       |

NOTES

<sup>1</sup>Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability. <sup>2</sup>LCC package only.

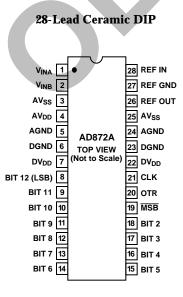

| Symbol            | DIP<br>Pin No. | LCC<br>Pin No.                            | Туре | Name and Function                                                                                                              |

|-------------------|----------------|-------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------|

| V <sub>INA</sub>  | 1              | 1                                         | AI   | (+) Analog Input Signal on the differential input amplifier.                                                                   |

| V <sub>INB</sub>  | 2              | 2                                         | AI   | (-) Analog Input Signal on the differential input amplifier.                                                                   |

| AV <sub>SS</sub>  | 3, 25          | 5, 40                                     | Р    | -5 V Analog Supply.                                                                                                            |

| $AV_{DD}$         | 4              | 6, 38                                     | Р    | +5 V Analog Supply.                                                                                                            |

| AGND              | 5, 24          | 9, 36                                     | Р    | Analog Ground.                                                                                                                 |

| DGND              | 6, 23          | 10                                        | Р    | Digital Ground.                                                                                                                |

| DV <sub>DD</sub>  | 7, 22          | 33                                        | Р    | +5 V Digital Supply.                                                                                                           |

| BIT 12 (LSB)      | 8              | 16                                        | DO   | Least Significant Bit.                                                                                                         |

| BIT 2-BIT 11      | 18-9           | 26-17                                     | DO   | Data Bits 2 through 11.                                                                                                        |

| MSB               | 19             | 29                                        | DO   | Inverted Most Significant Bit. Provides twos complement output data format.                                                    |

| OTR               | 20             | 30                                        | DO   | Out of Range is Active HIGH on the leading edge of Code 0 or the trailing edge of Code 4096. See Output Data Format Table III. |

| CLK               | 21             | 31                                        | DI   | Clock Input. The AD872A will initiate a conversion on the rising edge of the clock input. See the Timing Diagram for details.  |

| REF OUT           | 26             | 41                                        | AO   | +2.5 V Reference Output. Tie to REF IN for normal operation.                                                                   |

| REF GND           | 27             | 42                                        | AI   | Reference Ground.                                                                                                              |

| REF IN            | 28             | 43                                        | AI   | Reference Input. +2.5 V input gives $\pm 1$ V full-scale range.                                                                |

| DRV <sub>DD</sub> | N/A            | 12, 32                                    | Р    | +5 V Digital Supply for the output drivers.                                                                                    |

| NC                | N/A            | 3, 4, 7, 8, 14, 15,<br>28, 35, 37, 39, 44 |      | No Connect.                                                                                                                    |

| DRGND             | N/A            | 11, 34                                    | Р    | Digital Ground for the output drivers. (See section on Power Supply Decoupling for details on $DRV_{DD}$ and $DRGND$ .)        |

| OEN               | N/A            | 13                                        | DI   | Output Enable. See the Three State Output Timing Diagram for details.                                                          |

| BIT 1             | N/A            | 27                                        | DO   | Most Significant Bit.                                                                                                          |

#### PIN DESCRIPTION

TYPE: AI = Analog Input; AO = Analog Output; DI = Digital Input; DO = Digital Output; P = Power; N/A = Not Available on 28-lead DIP. Only available on 44-terminal surface mount package.

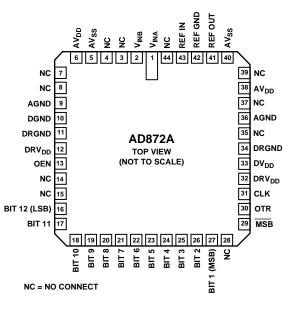

#### **PIN CONFIGURATIONS**

44-Terminal LCC

#### **DEFINITIONS OF SPECIFICATIONS**

#### LINEARITY ERROR (INL)

Linearity error refers to the deviation of each individual code from a line drawn from "negative full scale" through "positive full scale." The point used as "negative full scale" occurs 1/2 LSB before the first code transition. "Positive full scale" is defined as a level 1 1/2 LSB beyond the last code transition. The deviation is measured from the middle of each particular code to the true straight line.

## DIFFERENTIAL LINEARITY ERROR (DNL, NO MISSING CODES)

An ideal ADC exhibits code transitions that are exactly 1 LSB apart. DNL is the deviation from this ideal value. Guaranteed no missing codes to 12-bit resolution indicates that all 4096 codes must be present over all operating ranges.

#### ZERO ERROR

The major carry transition should occur for an analog value 1/2 LSB below analog common. Zero error is defined as the deviation of the actual transition from that point. The zero error and temperature drift specify the initial deviation and maximum change in the zero error over temperature.

#### GAIN ERROR

The first code transition should occur for an analog value 1/2 LSB above nominal negative full scale. The last transition should occur for an analog value 1 1/2 LSB below the nominal positive full scale. Gain error is the deviation of the actual difference between first and last code transitions and the ideal difference between first and last code transitions.

#### **TEMPERATURE DRIFT**

The temperature drift for zero error and gain error specifies the maximum change from the initial (+25°C) value to the value at  $T_{MIN}$  or  $T_{MAX}.$

#### POWER SUPPLY REJECTION

The specifications show the maximum change in the converter's full scale as the supplies are varied from nominal to min/max values.

#### **APERTURE JITTER**

Aperture jitter is the variation in aperture delay for successive samples and is manifested as noise on the input to the A/D.

#### **APERTURE DELAY**

Aperture delay is a measure of the Track-and-Hold Amplifier (THA) performance and is measured from the rising edge of the clock input to when the input signal is held for conversion.

#### **OVERVOLTAGE RECOVERY TIME**

Overvoltage recovery time is defined as that amount of time required for the ADC to achieve a specified accuracy after an overvoltage (50% greater than full-scale range), measured from the time the overvoltage signal reenters the converter's range.

#### DYNAMIC SPECIFICATIONS

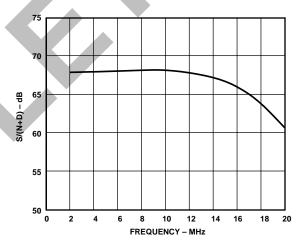

#### SIGNAL-TO-NOISE AND DISTORTION (S/N+D) RATIO

S/N+D is the ratio of the rms value of the measured input signal to the rms sum of all other spectral components below the Nyquist frequency, including harmonics but excluding dc. The value for S/N+D is expressed in decibels.

#### TOTAL HARMONIC DISTORTION (THD)

THD is the ratio of the rms sum of the first six harmonic components to the rms value of the measured input signal and is expressed as a percentage or in decibels.

#### **INTERMODULATION DISTORTION (IMD)**

With inputs consisting of sine waves at two frequencies, fa and fb, any device with nonlinearities will create distortion products, of order (m + n), at sum and difference frequencies of mfa  $\pm$  nfb, where m, n = 0, 1, 2, 3... Intermodulation terms are those for which m or n is not equal to zero. For example, the second order terms are (fa + fb) and (fa - fb), and the third order terms are (2 fa + fb), (2 fa - fb), (fa + 2 fb) and (2 fb - fa). The IMD products are expressed as the decibel ratio of the rms sum of the measured input signals to the rms sum of the distortion terms. The two signals are of equal amplitude and the peak value of their sums is -0.5 dB from full scale. The IMD products are normalized to a 0 dB input signal.

#### **FULL-POWER BANDWIDTH**

The full-power bandwidth is that input frequency at which the amplitude of the reconstructed fundamental is reduced by 3 dB for a full-scale input.

#### SPURIOUS FREE DYNAMIC RANGE

The difference, in dB, between the rms amplitude of the input signal and the peak spurious signal.

#### **ORDERING GUIDE**

| Model                 | Temperature Range | Package Option <sup>1</sup> |

|-----------------------|-------------------|-----------------------------|

| AD872AJD              | 0°C to +70°C      | D-28                        |

| AD872AJE              | 0°C to +70°C      | E-44A                       |

| AD872ASD <sup>2</sup> | -55°C to +125°C   | D-28                        |

| AD872ASE <sup>2</sup> | -55°C to +125°C   | E-44A                       |

NOTES

<sup>1</sup>D = Ceramic DIP, E = Leadless Ceramic Chip Carrier. <sup>2</sup>MIL-STD-883 version will be available; contact factory.

### Dynamic Characteristics-Sample Rate: 10 MSPS-AD872A

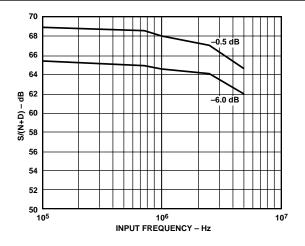

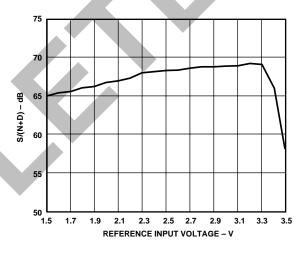

Figure 2. AD872A S/(N+D) Input Frequency

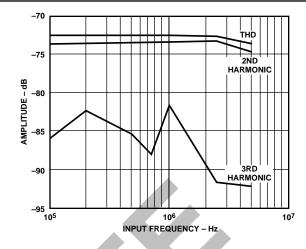

Figure 3. AD872A Distortion vs. Input Frequency, Full-Scale Input

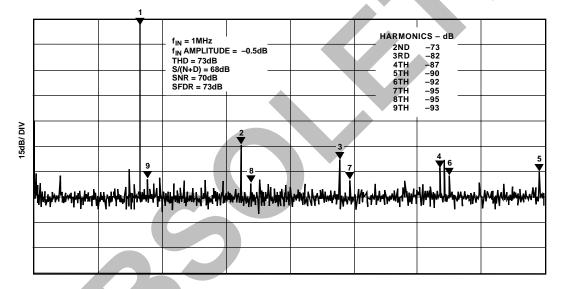

Figure 4. AD872A Typical FFT,  $f_{IN} = 1$  MHz,  $f_{IN}$  Amplitude = -0.5 dB

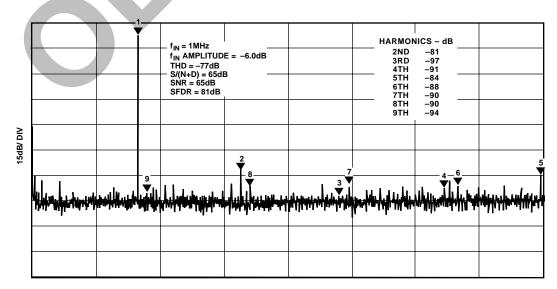

Figure 5. AD872A Typical FFT,  $f_{IN} = 1$  MHz,  $f_{IN}$  Amplitude = -6 dB

### AD872A–Dynamic Characteristics–Sample Rate: 10 MSPS

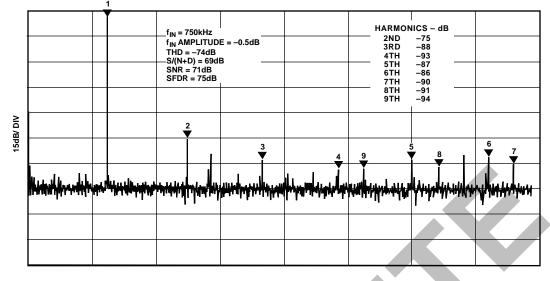

Figure 6. AD872A Typical FFT,  $f_{IN} = 750 \text{ kHz}$

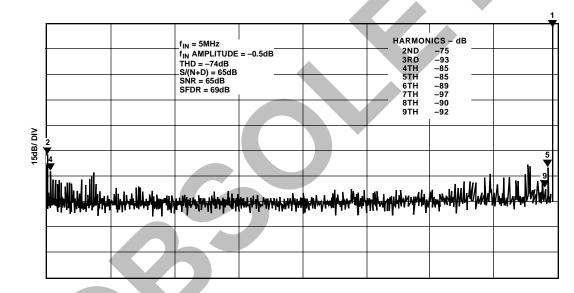

Figure 7. AD872A Typical FFT, f<sub>IN</sub> = 5 MHz

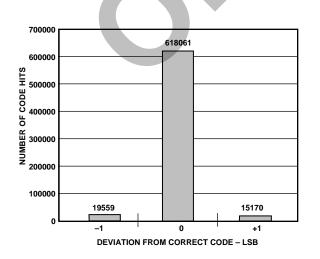

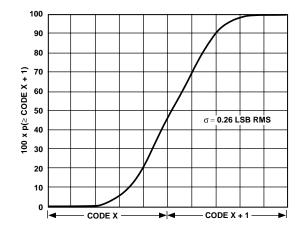

Figure 8. AD872A Output Code Histogram for DC Input

Figure 9. AD872A Code Probability at a Transition

#### THEORY OF OPERATION

The AD872A is implemented using a 4-stage pipelined multiple flash architecture. A differential input track-and-hold amplifier (THA) acquires the input and converts the input voltage into a differential current. A 4-bit approximation of the input is made by the first flash converter, and an accurate analog representation of this 4-bit guess is generated by a digital-to-analog converter. This approximation is subtracted from the THA output to produce a remainder, or residue. This residue is then sampled and held by the second THA, and a 4-bit approximation is generated and subtracted by the second stage. Once the second THA goes into hold, the first stage goes back into track to acquire a new input signal. The third stage provides a 3-bit approximation/subtraction operation, and produces the final residue, which is passed to a final 4-bit flash converter. The 15 output bits from the 4 flash converters are accumulated in the correction logic block, which adds the bits together using the appropriate correction algorithm, to produce the 12-bit output word. The digital output, together with overrange indicator, is latched into an output buffer to drive the output pins.

The additional THA inserted in each stage of the AD872A architecture allows pipelining of the conversion. In essence, the converter is converting multiple inputs simultaneously, processing them through the converter chain serially. This means that while the converter is capable of capturing a new input sample every clock cycle, it actually takes three clock cycles for the con version to be fully processed and appear at the output. This "pipeline delay" is often referred to as latency, and is not a concern in most applications, however there are some cases where it may be a consideration. For example, some applications call for the A/D converter to be placed in a high speed feedback loop, where its input is servoed to provide a desired result at the digital output (e.g., offset calibration or zero restoration in video applications). In these cases the three clock cycle delay through the pipeline must be accounted for in the loop stability calculations. Also, because the converter is working on three conversions simultaneously, major disruptions to the part (such as a large glitch on the supplies or reference) may corrupt three data samples. Finally, there will be a minimum clock rate below which the THA droop corrupts the signal in the pipeline. In the case of the AD872A, this minimum clock rate is 10 kHz.

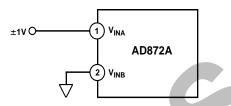

The high impedance differential inputs of the AD872A allow a variety of input configurations (see APPLYING THE AD872A), The AD872A converts the voltage difference between the V<sub>INA</sub> and V<sub>INB</sub> pins. For single-ended applications, one input pin (V<sub>INA</sub> or V<sub>INB</sub>) may be grounded, but even in this case the differential input can provide a performance boost: for example, for an input coming from a coaxial cable, V<sub>INB</sub> can be tied to the shield ground, allowing the AD872A to reject shield noise as common mode. The high input impedance of the device minimizes external driving requirements and allows the user to externally select the appropriate termination impedance for the application.

The AD872A clock circuitry uses both edges of the clock in its internal timing circuitry (see spec page for exact timing requirements). The AD872A samples the analog input on the rising edge of the clock input. During the clock low time (between the falling edge and rising edge of the clock) the input THA is in track mode; during the clock high time it is in hold. System disturbances just prior to the rising edge of the clock may cause the part to acquire the wrong value, and should be minimized.

While the part uses both clock edges for its timing, jitter is only a significant issue for the rising edge of the clock (see CLOCK INPUT section).

#### APPLYING THE AD872A ANALOG INPUTS

The AD872A features a high impedance differential input that can readily operate on either single-ended or differential input signals. Table I summarizes the nominal input voltage span for both single-ended and differential modes, assuming a 2.5 V reference input.

| Table I. | Input | Voltage | Span |

|----------|-------|---------|------|

|----------|-------|---------|------|

|              | V <sub>INA</sub> | V <sub>INB</sub> | V <sub>INA</sub> -V <sub>INB</sub>                       |

|--------------|------------------|------------------|----------------------------------------------------------|

| Single-Ended | +1 V             | GND<br>GND       | +1 V (Positive Full Scale)<br>-1 V (Negative Full Scale) |

| Differential | +0.5 V           | -0.5 V           | +1 V (Positive Full Scale)                               |

|              | -0.5 V           | +0.5 V           | -1 V (Negative Full Scale)                               |

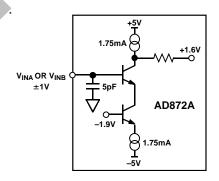

Figure 10 shows an approximate model for the analog input circuit. As this model indicates, when the input exceeds 1.6 V (with respect to AGND), the input device may saturate, causing the input impedance to drop substantially and significantly reducing the performance of the part. Input compliance in the negative direction is somewhat larger, showing virtually no degradation in performance for inputs as low as -1.9 V.

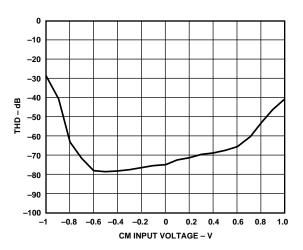

Figure 10. AD872A Equivalent Analog Input Circuit Figure 11 illustrates the effect of varying the common-mode voltage of a -0.5 dB input signal on total harmonic distortion.

Figure 11. AD872A Total Harmonic Distortion vs. CM Input Voltage,  $f_{IN} = 1$  MHz, FS = 10 MSPS

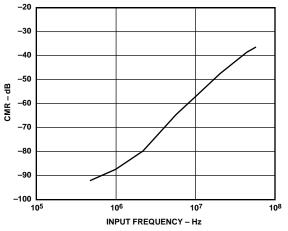

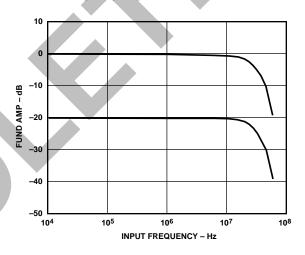

Figure 12 shows the common-mode rejection performance vs. frequency for a 1 V p-p common-mode input. This excellent common-mode rejection over a wide bandwidth affords the user the opportunity to eliminate many potential sources of input noise as common mode by using the differential input structure of the AD872A.

Figure 12. Common-Mode Rejection vs. Input Frequency, 1 V p-p Input

Figures 13 and 14 illustrate typical input connections for singleended inputs.

Figure 13. AD872A Single-Ended Input Connection

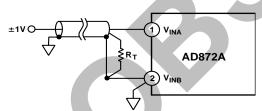

Figure 14. AD872A Single-Ended Input Connection Using a Shielded Cable

The cable shield is used as a ground connection for the  $V_{\rm INB}$  input, providing the best possible rejection of the cable noise from the input signal. Note also that the high input impedance of the AD872A allows the user to select the termination impedance, be it 50 ohms, or some other value. Furthermore, unlike many flash converters, most AD872A applications will not require an external buffer amplifier. If such an amplifier is required, we suggest either the AD811 or AD9617.

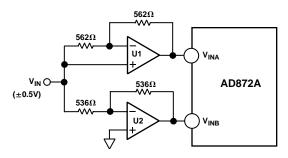

Figure 15 illustrates how external amplifiers may be used to convert a single-ended input into a differential signal. The resistor values of 536  $\Omega$  and 562  $\Omega$  were selected to provide optimum phase matching between U1 and U2.

Figure 15. Single-Ended to Differential Connections; U1, U2 = AD811 or AD9617

The use of the differential input signal can help to minimize even-order distortion from the input THA where performance beyond -70 dB is desired.

Figure 16 shows the AD872A large signal (-0.5 dB) and small signal (-20 dB) frequency response.

Figure 16. Full Power (–0.5 dB) and Small Signal Response (–20 dB) vs. Input Frequency

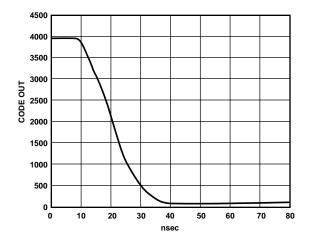

The AD872A's wide input bandwidth facilitates rapid acquisition of transient input signals: the input THA can typically settle to 12-bit accuracy from a full-scale input step in less than 40 ns. Figure 17 illustrates the typical acquisition of a full-scale input step.

Figure 17. Typical AD872A Settling Time

The wide input bandwidth and superior dynamic performance of the input THA make the AD872A suitable for undersampling applications where the input frequency exceeds half the sample frequency. The input THA is designed to recover rapidly from input overdrive conditions, returning from a 50% overdrive in less than 40 ns.

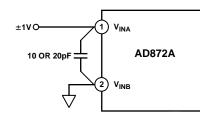

Because of the THA's exceptionally wide input bandwidth, some users may find the AD872A is sensitive to noise at frequencies from 10 MHz to 50 MHz that other converters are incapable of responding to. This sensitivity can be mitigated by careful use of the differential inputs (see previous paragraphs). Additionally, Figure 18 shows how a small capacitor (10 pF-20 pF for 50  $\Omega$  terminated inputs) may be placed between  $V_{\rm INA}$  and  $V_{\rm INB}$  to help reduce high frequency noise in applications where limiting the input bandwidth is acceptable.

#### Figure 18. Optional High Frequency Noise Reduction

The AD872A will contribute its own wideband thermal noise. As a result of the integrated wideband noise (0.26 LSB rms, referred-to-input), applying a dc analog input may produce more than one code at the output. A histogram of the ADC output codes, for a dc input voltage, will be between one and three codes wide, depending on how well the input is centered on a given code and how many samples are taken. Figure 8 shows a typical AD872A code histogram, and Figure 9 illustrates the AD872A's transition noise.

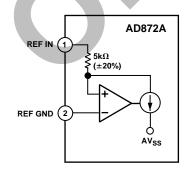

#### **REFERENCE INPUT**

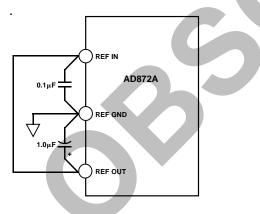

The nominal reference input should be 2.5 V, taken with respect to REFERENCE GROUND (REF GND). Figure 19 illustrates the equivalent model for the reference input: there is no clock or signal-dependent activity associated with the reference input circuitry, therefore, no "kickback" into the reference.

However, in order to realize the lowest noise performance of the AD872A, care should be taken to minimize noise at the reference input.

The AD872A's reference input impedance is equal to 5 k $\Omega$  (±20%), and its effective noise bandwidth is 10 MHz, with a referred-to-input noise gain of 0.8. For example, the internal reference, with an rms noise of 28  $\mu V$  (using an external 1  $\mu F$  capacitor), contributes 24  $\mu V$  (0.05 LSB) of noise to the transfer function of the AD872A.

The full-scale peak-to-peak input voltage is a function of the reference voltage, according to the equation:

$$(V_{INA} = V_{INB})$$

Full Scale =  $0.8 \times (V_{RFF} - REF GND)$

Note that the AD872A's performance was optimized for a 2.5 V reference input: performance may degrade somewhat for other reference voltages. Figure 20 illustrates the S/(N+D) performance vs. reference voltage for a 1 MHz, -0.5 dB input signal. Note also that if the reference is changed during a conversion, all three conversions in the pipeline will be invalidated.

Figure 20. S/(N+D) vs. Reference Input Voltage,  $f_{IN} = 1 \text{ MHz}$ , FS = 10 MHz

Table II summarizes various 2.5 V references suitable for use with the AD872A, including the onboard bandgap reference (see REFERENCE OUTPUT section).

Table II. Suitable 2.5 V References

|          | Drift (ppm/°C) | Initial Accuracy % |

|----------|----------------|--------------------|

| REF43B   | 6 (max)        | 0.2                |

| AD680JN  | 10 (max)       | 0.4                |

| Internal | 30 (typ)       | 0.4                |

If an external reference is connected to REF IN, REF OUT must be connected to +5 V. This should lower the current in REF GND to less than 350  $\mu$ A and eliminate the need for a 1  $\mu$ F capacitor, although decoupling the reference for noise reduction purposes is recommended.

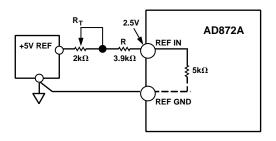

Alternatively, Figure 21 shows how the AD872A may be driven from other references by use of an external resistor. The external resistor forms a resistor divider with the on-chip 5 k $\Omega$  resistor to realize 2.5 V at the reference input pin (REF IN). A trim potentiometer is needed to accommodate the tolerance of the AD872A's 5 k $\Omega$  resistor.

Figure 21. Optional +5 V Reference Input Circuit

#### **REFERENCE GROUND**

The REF GND pin provides the reference point for both the reference input, and the reference output. When the internal reference is operating, it will draw approximately 500  $\mu$ A of current through the reference ground, so a low impedance path to the external common is desirable. The AD872A can tolerate a fairly large difference between REF GND and AGND, up to +1 V, without any performance degradation.

#### **REFERENCE OUTPUT**

The AD872A features an onboard, curvature compensated bandgap reference that has been laser trimmed for both absolute value and temperature drift. The output stage of the reference was designed to allow the use of an external capacitor to limit the wideband noise. As Figure 22 illustrates, a 1  $\mu$ F capacitor on the reference output is required for stability of the reference output buffer. Note: If used, an external reference may become unstable with this capacitor in place.

Figure 22. Typical Reference Decoupling Connection

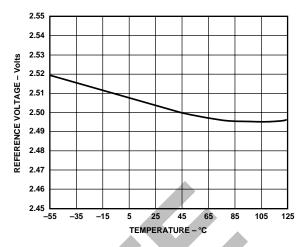

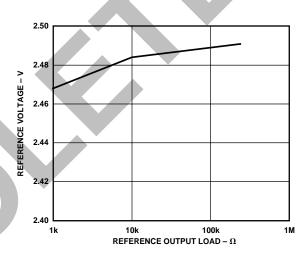

With this capacitor in place, the noise on the reference output is approximately 28  $\mu V$  rms at room temperature. Figure 23 shows the typical temperature drift performance of the reference, while Figure 24 illustrates the variation in reference voltage with load currents.

The output stage is designed to provide at least 2 mA of output current, allowing a single reference to drive up to four AD872As, or other external loads. The power supply rejection of the reference is better than -54 dB at dc.

Figure 23. Reference Output Voltage vs. Temperature

Figure 24. Reference Output Voltage vs. Output Load

#### **DIGITAL OUTPUTS**

In 28-lead packages, the AD872A output data is presented in twos complement format. Table III indicates offset binary and twos complement output for various analog inputs.

**Table III. Output Data Format**

| Analog Input                       | Digital Output |                 |     |  |

|------------------------------------|----------------|-----------------|-----|--|

| V <sub>INA</sub> -V <sub>INB</sub> | Offset Binary  | Twos Complement | OTR |  |

| ≥0.999756 V                        | 1111 1111 1111 | 0111 1111 1111  | 1   |  |

| 0.999268 V                         | 1111 1111 1111 | 0111 1111 1111  | 0   |  |

| 0 V                                | 1000 0000 0000 | 0000 0000 0000  | 0   |  |

| -1 V                               | 0000 0000 0000 | 1000 0000 0000  | 0   |  |

| –1.000244 V                        | 0000 0000 0000 | 1000 0000 0000  | 1   |  |

Users requiring offset binary encoding may simply invert the  $\overline{\text{MSB}}$  pin. In the 44-terminal surface mount packages, both MSB and  $\overline{\text{MSB}}$  bits are provided.

The AD872A features a digital out-of-range (OTR) bit that goes high when the input exceeds positive full scale or falls below negative full scale. As Table III indicates, the output bits will be set appropriately according to whether it is an out-of-range high condition or an out-of-range low condition. Note that if the input is driven beyond +1.5 V, the digital outputs may not stay at +FS, but may actually fold back to midscale.

The AD872A's CMOS digital output drivers are sized to provide sufficient output current to drive a wide variety of logic families. However, large drive currents tend to cause glitches on the supplies and may affect S/(N+D) performance. Applications requiring the AD872A to drive large capacitive loads or large fanout may require additional decoupling capacitors on DRV<sub>DD</sub> and DV<sub>DD</sub>. In extreme cases, external buffers or latches could be used.

#### THREE-STATE OUTPUTS

The 44-terminal surface mount AD872A offers three-state outputs. The digital outputs can be placed into a three-state mode by pulling the OUTPUT ENABLE (OEN) pin LOW. Note that this function is not intended to be used to pull the AD872A on and off a bus at 10 MHz. Rather, it is intended to allow the ADC to be pulled off the bus for evaluation or test modes. Also, to avoid corruption of the sampled analog signal during conversion (3 clock cycles), it is highly recommended that the AD872A be placed on the bus prior to the first sampling.

Figure 25. Three-State Output Timing Diagram

For timing budgetary purposes, the typical access and float delay times for the AD872A are 50 ns.

#### **CLOCK INPUT**

The AD872A internal timing control uses the two edges of the clock input to generate a variety of internal timing signals. The optimal clock input should have a 50% duty cycle; however, sensitivity to duty cycle is significantly reduced for clock rates of less than 10 megasamples per second.

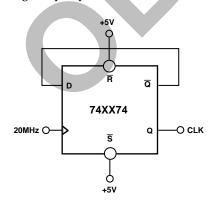

Figure 26. Divide-by-Two Clock Circuit

Due to the nature of on-chip compensation circuitry, the duty cycle should be maintained between 40% and 60% even for clock rates less than 10 MSPS. One way to realize a 50% duty cycle clock is to divide down a clock of higher frequency, as shown in Figure 26.

In this case, a 20 MHz clock is divided by 2 to produce the 10 MHz clock input for the AD872A. In this configuration, the duty cycle of the 20 MHz clock is irrelevant.

The input circuitry for the CLKIN pin is designed to accommodate both TTL and CMOS inputs. The quality of the logic input, particularly the rising edge, is critical in realizing the best possible jitter performance for the part: the faster the rising edge, the better the jitter performance.

As a result, careful selection of the logic family for the clock driver, as well as the fanout and capacitive load on the clock line, is important. Jitter-induced errors become more pronounced at higher frequency, large amplitude inputs, where the input slew rate is greatest.

The AD872A is designed to support a sampling rate of 10 MSPS; running at slightly faster clock rates may be possible, although at reduced performance levels. Conversely, some slight performance improvements might be realized by clocking the AD872A at slower clock rates. Figure 27 presents the S/(N+D) vs. clock frequency for a 1 MHz analog input.

Figure 27. Typical S/(N+D) vs. Clock Frequency,  $f_{IN} = 1$  MHz, Full-Scale Input

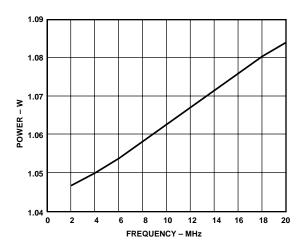

The power dissipated by the correction logic and output buffers is largely proportional to the clock frequency; running at reduced clock rates provides a slight reduction in power consumption. Figure 28 illustrates this tradeoff.

Figure 28. Typical Power Dissipation vs. Clock Frequency

#### ANALOG SUPPLIES AND GROUNDS

The AD872A features separate analog and digital supply and ground pins, helping to minimize digital corruption of sensitive analog signals. In general,  $AV_{SS}$  and  $AV_{DD}$ , the analog supplies, should be decoupled to AGND, the analog common, as close to the chip as physically possible. Care has been taken to minimize the signal dependence of the power supply currents; however, the analog supply currents will be proportional to the reference input. With REFIN at 2.5 V, the typical current into  $AV_{DD}$  is 85 mA, while the typical current out of  $AV_{SS}$  is 115 mA. Typically, 30 mA will flow into the AGND pin.

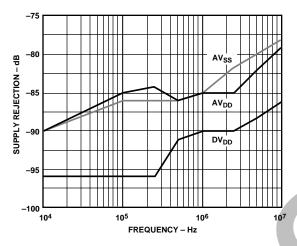

Careful design and the use of differential circuitry provide the AD872A with excellent rejection of power supply noise over a wide range of frequencies, as illustrated in Figure 29.

Figure 29. Power Supply Rejection vs. Frequency, 100 mV p-p Signal on Power Supplies

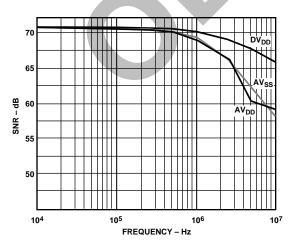

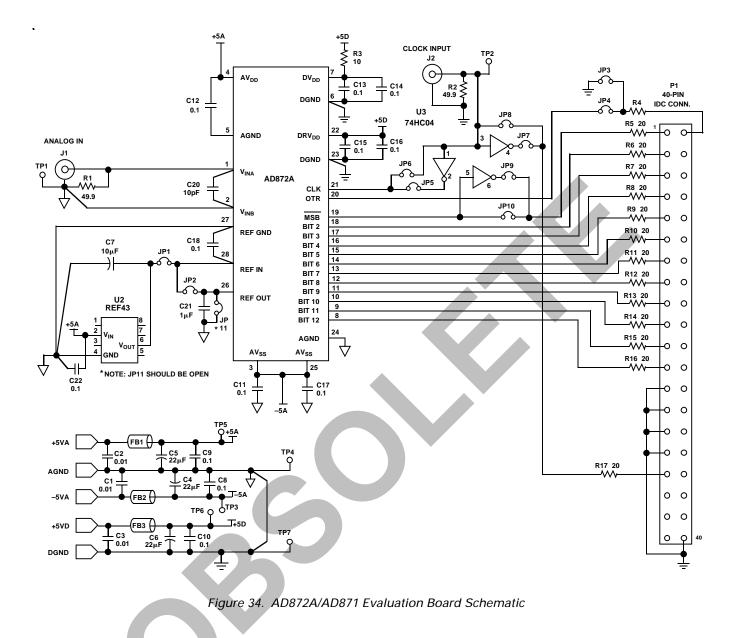

Figure 30 shows the degradation in SNR resulting from 100 mV of power supply ripple at various frequencies. As Figure 30 shows, careful decoupling is required to realize the specified dynamic performance. Figure 34 demonstrates the recommended decoupling strategy for the supply pins. Note that in extremely noisy environments, a more elaborate supply filtering scheme may be necessary.

Figure 30. SNR vs. Supply Noise Frequency  $(f_{IN} = 1 \text{ MHz})$

#### DIGITAL SUPPLIES AND GROUNDS

The digital activity on the AD872A chip falls into two general categories: CMOS correction logic, and CMOS output drivers. The internal correction logic draws relatively small surges of current, mainly during the clock transitions; in the 44-terminal package, these currents flow through pins DGND and  $DV_{DD}$ . The output drivers draw large current impulses while the output bits are changing. The size and duration of these currents are a function of the load on the output bits: large capacitive loads are to be avoided. In the 44-terminal package, the output drivers are supplied through dedicated pins DRGND and DRV<sub>DD</sub>. Pin count constraints in the 28-lead packages require that the digital and driver supplies share package pins (although they have separate bond wires and on-chip routing). The decoupling shown in Figure 34 is appropriate for a reasonable capacitive load on the digital outputs (typically 20 pF on each pin). Applications involving greater digital loads should consider increasing the digital decoupling proportionately, and/or using external buffers/ latches.

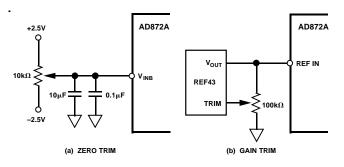

#### APPLICATIONS OPTIONAL ZERO AND GAIN TRIM

The AD872A is factory trimmed to minimize zero error, gain error and linearity errors. In some applications the zero and gain errors of the AD872A need to be externally adjusted to zero. If required, both zero error and gain error can be trimmed with external potentiometers as shown in Figure 31. Note that gain error adjustments must be made with an external reference.

Zero trim should be adjusted first. Connect  $V_{INA}$  to ground and adjust the 10 k $\Omega$  potentiometer such that a nominal digital output code of 0000 0000 0000 (twos complement output) exists. Note that the zero trim should be decoupled and that the accuracy of the  $\pm 2.5$  V reference signals will directly affect the offset.

Gain error may then be calibrated by adjusting the REF IN voltage. The REF IN voltage should be adjusted such that a +1 V input on V<sub>INA</sub> results in the digital output code 01111 1111 1111 (twos complement output).

Figure 31. Zero and Gain Error Trims

#### DIGITAL OFFSET CORRECTION

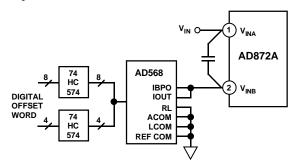

The AD872A provides differential inputs that may be used to correct any offset voltages on the analog input. For applications where the input signal contains a dc offset, it may be advantageous to apply a nulling voltage to the  $V_{\rm INB}$  input. Applying a voltage equal to the dc offset will maximize the full-scale input range and therefore the dynamic range. Offsets ranging from -0.7 V to +0.5 V can be corrected.

Figure 32 shows how a dc offset can be applied using the AD568 12-bit, high speed digital-to-analog converter (DAC). This circuit can be used for applications requiring offset adjustments on every clock cycle. The AD568 connection scheme is used to provide a -0.512 V to +0.512 V output range. The offset voltage must be stable on the rising edge of the AD872A clock input.

Figure 32. Offset Correction Using the AD568

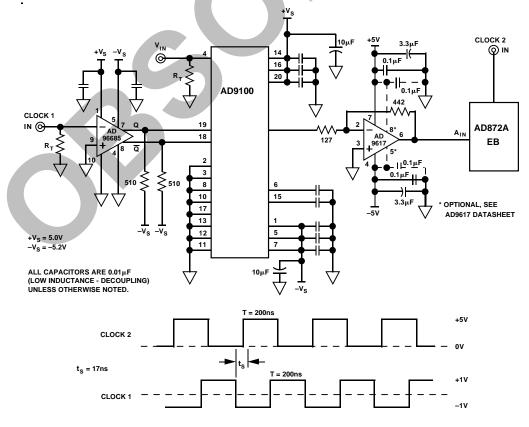

**UNDERSAMPLING USING THE AD872A AND AD9100** The AD872A's on-chip THA optimizes transient response while maintaining low noise performance. For super-Nyquist (undersampling) applications it may be necessary to use an external THA with fast track-mode slew rate and hold mode settling time. An excellent choice for this application is the AD9100, an ultrahigh speed track-and-hold amplifier. In order to maximize the spurious free dynamic range of the circuit in Figure 33 it is advantageous to present a small signal to the input of the AD9100 and then amplify the output to the AD872A's full-scale input range. This can be accomplished with a low distortion, wide bandwidth amplifier such as the AD9617. The circuit uses a gain of 3.5 to optimize S/(N+D).

For small scale input signals (-20 dB, -40 dB), the AD872A performs better without the track-and-hold because slew-limiting effects are no longer dominant. To gain the advantages of the added track-and-hold, it is important to give the AD872A a full-scale input.

An alternative to the configuration presented above is to use the AD9101 track-and-hold amplifier. The AD9101 provides a built-in post amplifier with a gain of 4, providing excellent ac characteristics in conjunction with a high level of integration.

As illustrated in Figure 33, it is necessary to skew the AD872A sample clock and the AD9100 sample/hold control. Clock skew  $(t_S)$  is defined as the time starting at the AD9100's transition into hold mode and ending at the moment the AD872A samples. The AD872A samples on the rising edge of the sample clock, and the AD9100 samples on the falling edge of the sample/hold control. The choice of  $t_S$  is primarily determined by the settling time of the AD9100. The droop rate of the AD9100 must also be taken into consideration. Using these values, the ideal  $t_S$  is 17 ns. When choosing clock sources, it is extremely important that the front end track-and-hold sample/hold control is given a very low jitter clock source. This is not as crucial for the AD872A sample clock, because it is sampling a dc signal.

Figure 33. Undersampling Using the AD872A and AD9100

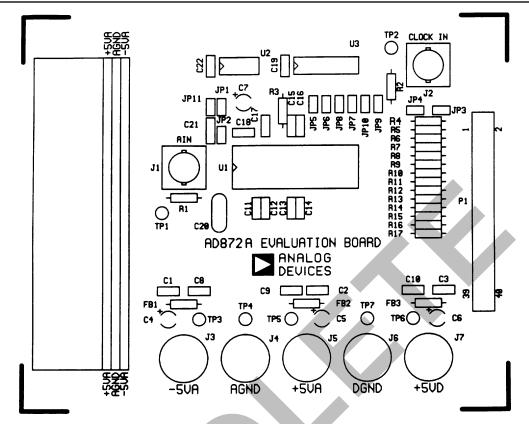

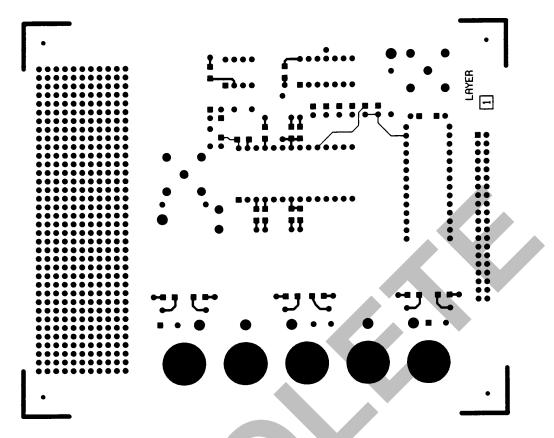

Figure 35. Silkscreen Layer PCB Layout (Not Shown to Scale)

| able IV. | Comp | onents | List |

|----------|------|--------|------|

|          |      |        |      |

Т

| Reference Designator | Description                             | Quantity |

|----------------------|-----------------------------------------|----------|

| R1, R2               | Resistor, 1%, Metal Film, 49.9 $\Omega$ | 2        |

| R3                   | Resistor, 1%, Metal Film, 10            | 1        |

| R4-R17               | Resistor, 1%, Metal Film, 20            | 14       |

| C1-C3                | SMD Chip Capacitor, 0.01 µF             | 3        |

| C4-C6                | Capacitor, Tantalum, 22 µF              | 3        |

| C7                   | Capacitor, Tantalum, 10 µF              | 1        |

| C8-C19, C22          | SMD Chip Capacitor, 0.1 µF              | 13       |

| C20                  | Capacitor, Mica, 10 pF                  | 1        |

| C21                  | Capacitor, Ceramic, 1 µF                | 1        |

| U1                   | AD872A                                  | 1        |

| U2                   | REF43B                                  | 1        |

| U3                   | 74HC04N                                 | 1        |

| FB1-FB3              | Ferrite Bead                            | 3        |

| J1, J2               | BNC Jack                                | 2        |

| JP2, 3, 5, 7, 10     | Jumpers                                 | 5        |

| JP1-JP11             | Headers                                 | 11       |

| P1                   | 40-Pin IDC Connector                    | 1        |

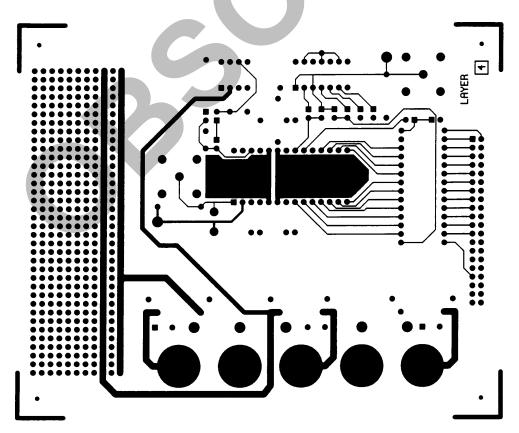

Figure 36. Component Side PCB Layout (Not Shown to Scale)

Figure 37. Solder Side PCB Layout (Not Shown to Scale)

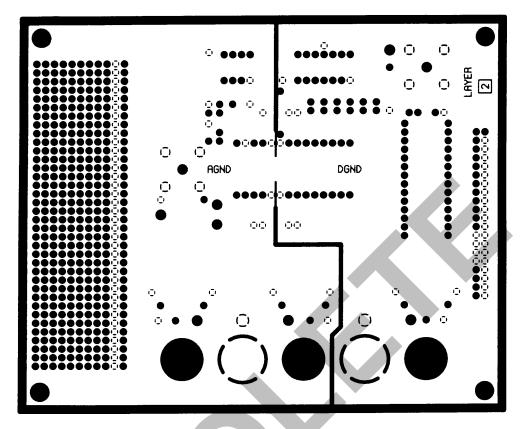

Figure 38. Ground Layer PCB Layout (Not Shown to Scale)

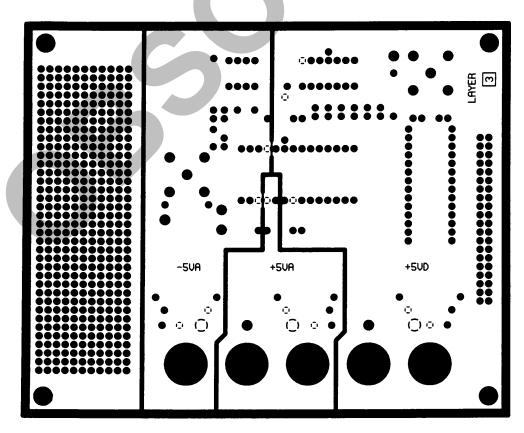

Figure 39. Power Layer PCB Layout (Not Shown to Scale)

#### **OUTLINE DIMENSIONS**

Dimensions shown in inches and (mm).