**BOARD LAYOUT AND ROUTING GUIDELINES**

### **TABLE OF CONTENTS**

#### 1.0 SCOPE

#### 2.0 PC BOARD REQUIREMENTS

- 2.1 MATERIAL THICKNESS

- 2.2 LAYOUT

#### 3.0 HIGH SPEED ROUTING

- 3.1 TRACE TO PAD ATTACHMENT

- 3.2 GROUD VIA PLACEMENT

- 3.3 IMPEDANCE MATCHING AT TRACE AND FOOTPRINT/PAD

- 3.4 HIGH SPEED REFERENCE PLANE ANTI-PAD

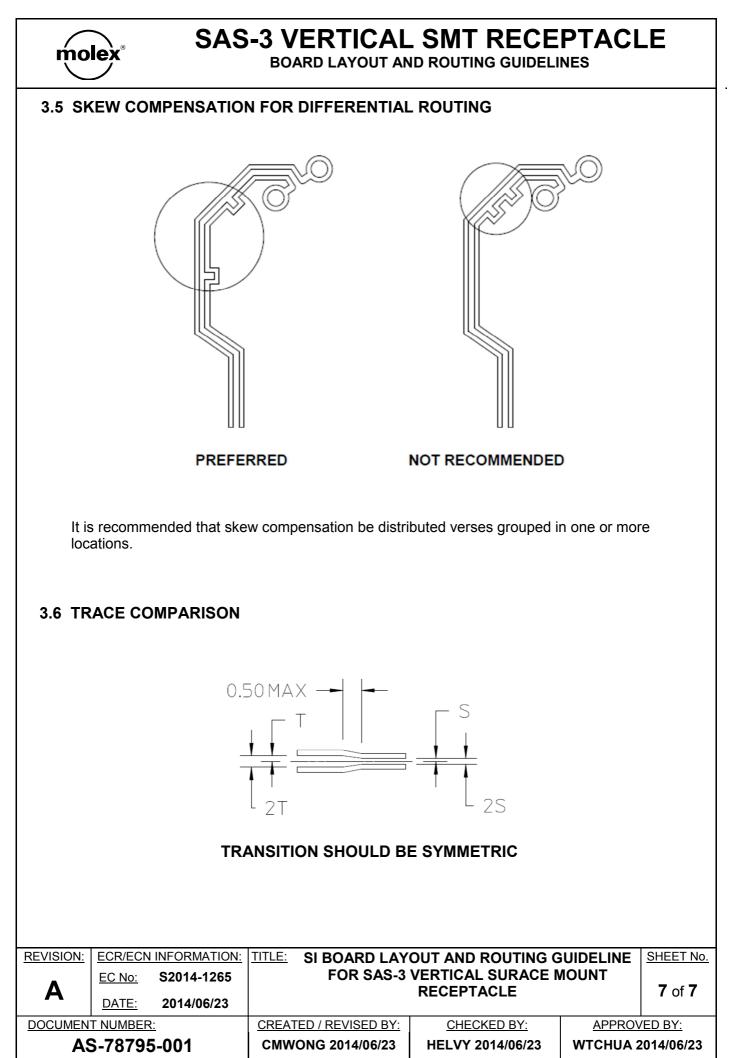

- 3.5 SKEW COMPENSATION FOR DIFFERENTIAL ROUTING

- 3.6 TRACE COMPARISON

| REVISION:        | ECR/ECN | I INFORMATION: | <b><u>TITLE:</u></b> SI BOARD LAYOUT AND ROUTING GUIDELINE |                  | SHEET No.         |                      |

|------------------|---------|----------------|------------------------------------------------------------|------------------|-------------------|----------------------|

| Α                | EC No:  | S2014-1265     | FOR SAS-3 VERTICAL SURACE MOUNT<br>RECEPTACLE              |                  |                   | <b>1</b> of <b>7</b> |

| ~                | DATE:   | 2014/06/23     |                                                            |                  |                   |                      |

| DOCUMENT NUMBER: |         |                | CREATED / REVISED BY:                                      | CHECKED BY:      | APPROVED BY:      |                      |

| AS-78795-001     |         |                | CMWONG 2014/06/23                                          | HELVY 2014/06/23 | WTCHUA 2014/06/23 |                      |

|                  |         |                |                                                            |                  | TEMPLATE FILENAME | : AS1704602.DOC      |

### 1.0 SCOPE

This board layout and routing guidelines cover the printed circuit board layout that can be used for the evaluation of high-speed signals using microstrip routing for 78795 series connector.

**Disclaimer:** Molex does not guarantee the performance of the final product to the information provided in this document. All information in this report is considered Molex proprietary and confidential. This guide is not intended as a substitute for engineering analysis where optimization for signal integrity (SI) performance can be critical.

### 2.0 PC BOARD REQUIREMENTS

### 2.1 MATERIAL THICKNESS

The recommended PC board thickness shall be 1.60mm. Suitable PC board material shall be glass epoxy (FR-4).

### 2.2 LAYOUT

The solder pads for the connector assembly must be precisely located to ensure proper placement and optimum performance of the connector assembly. Refer to the applicable Sales Drawing for the recommended solder pad pattern, dimensions and tolerances.

| REVISION:                         | ECR/ECN | INFORMATION: | TITLE: SI BOARD LAYOUT AND ROUTING GUIDELINE |                                                 | SHEET No.         |                      |

|-----------------------------------|---------|--------------|----------------------------------------------|-------------------------------------------------|-------------------|----------------------|

| A                                 | EC No:  | S2014-1265   | FOR SAS-3                                    | FOR SAS-3 VERTICAL SURACE MOUNT<br>RECEPTACLE 2 |                   | <b>2</b> of <b>7</b> |

|                                   | DATE:   | 2014/06/23   |                                              |                                                 |                   |                      |

| DOCUMENT NUMBER:                  |         |              | CREATED / REVISED BY:                        | CHECKED BY:                                     | APPROVED BY:      |                      |

| AS-78795-001                      |         |              | CMWONG 2014/06/23                            | HELVY 2014/06/23                                | WTCHUA 2014/06/23 |                      |

| TEMPLATE FILENAME: A\$1704602.DOC |         |              |                                              |                                                 |                   |                      |

**BOARD LAYOUT AND ROUTING GUIDELINES**

### 3.0 HIGH SPEED ROUTING

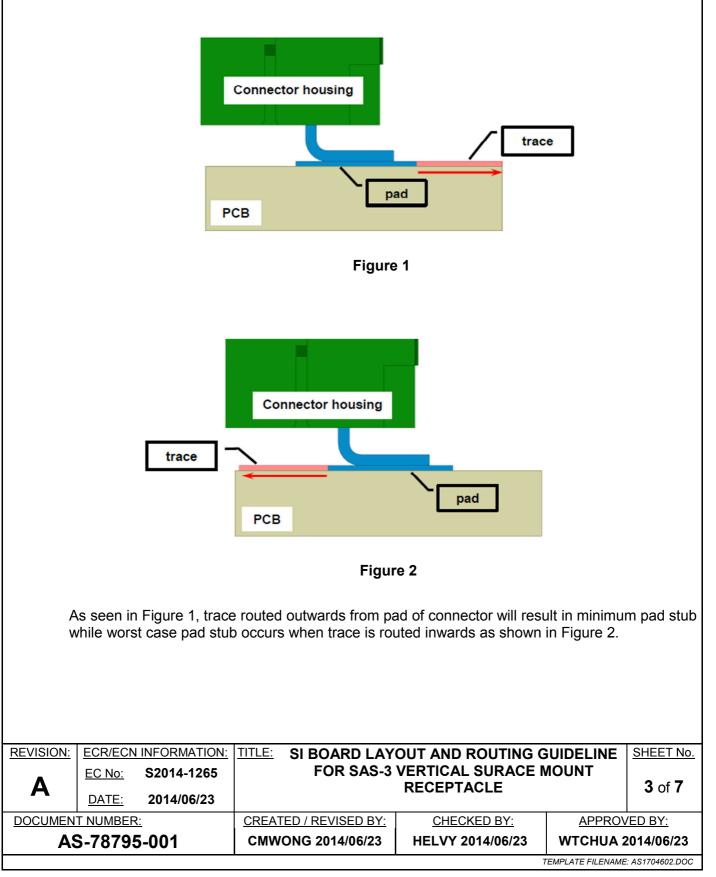

### 3.1 TRACE TO PAD ATTACHMENT

There are several ways to connect the traces to their corresponding signal pads. Two possible methods are illustrated in Figures 1 and 2.

**BOARD LAYOUT AND ROUTING GUIDELINES**

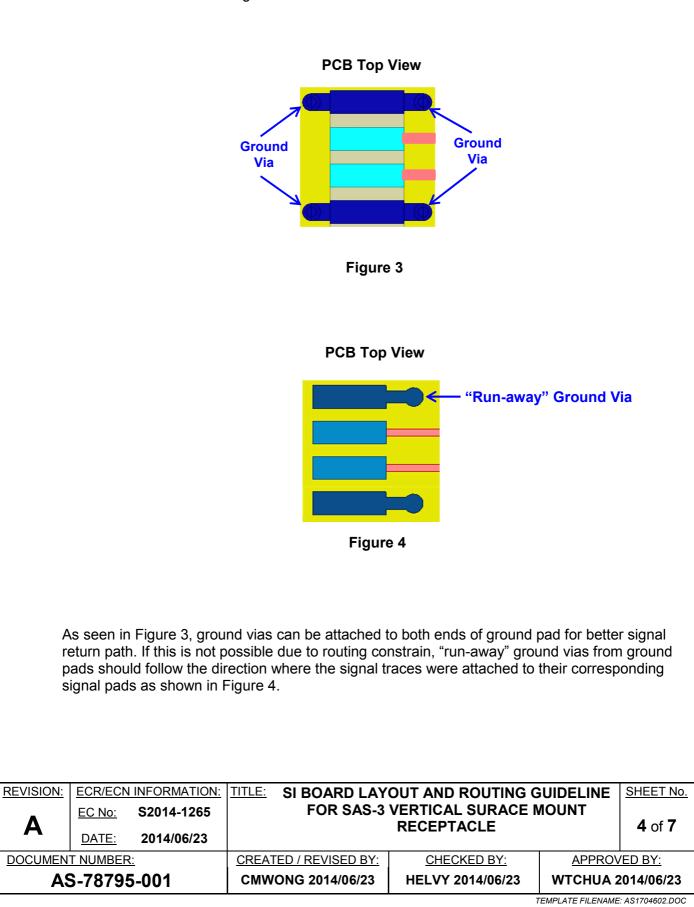

### 3.2 GROUND VIA PLACEMENT

There are several ways to connect ground vias to their corresponding ground pads. Two possible methods are illustrated in Figures 3 and 4.

**BOARD LAYOUT AND ROUTING GUIDELINES**

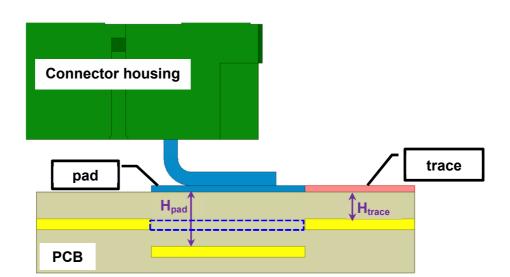

### 3.3 IMPEDANCE MATCHING AT TRACE AND FOOTPRINT/PAD

Impedance matching is critical to improve and optimize SI performance.

All traces and pad should design to obtain single-end  $50\Omega$  or differential  $100\Omega$  at application.

This could be done by controlling distance between trace  $(H_{trace})$  and pad  $(H_{pad})$  with reference to their ground return. This is illustrated in Figure 5.

When the trace width of pad equals to trace,  $H_{trace}$  equals  $H_{pad}$ . If pad width is wider than trace,  $H_{pad} > H_{trace}$ . This is to eliminate excessive capacitive coupling at pad region.

Figure 5

| REVISION:        | ECR/ECN                | INFORMATION:             | TITLE: SI BOARD LAYOUT AND ROUTING GUIDELINE |                                 | SHEET No.           |                      |

|------------------|------------------------|--------------------------|----------------------------------------------|---------------------------------|---------------------|----------------------|

| Α                | <u>EC No:</u><br>DATE: | S2014-1265<br>2014/06/23 | FOR SAS-3                                    | VERTICAL SURACE I<br>RECEPTACLE | MOUNT               | <b>5</b> of <b>7</b> |

| DOCUMENT NUMBER: |                        |                          | CREATED / REVISED BY:                        | CHECKED BY:                     | APPROV              | /ED BY:              |

| AS-78795-001     |                        |                          | CMWONG 2014/06/23                            | HELVY 2014/06/23                | WTCHUA 2            | 2014/06/23           |

|                  |                        |                          |                                              |                                 | TEMPI ATE EII ENAME | · AS1704602 DOC      |

**BOARD LAYOUT AND ROUTING GUIDELINES**

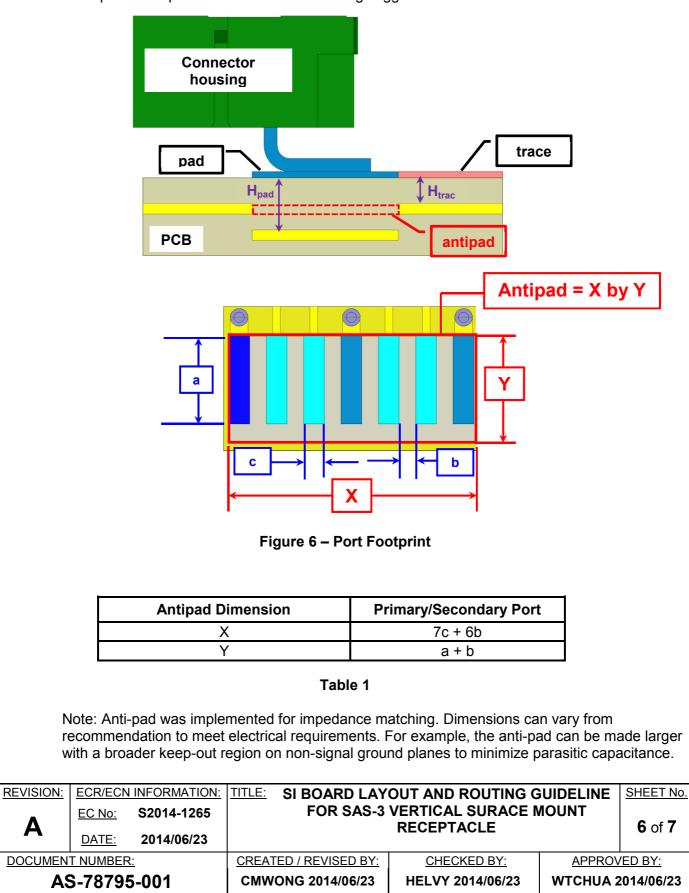

### 3.4 HIGH SPEED REFERENCE PLANE ANTI-PAD

An antipad or copper cutout region, shown in Figure 6, is needed to obtain desirable  $H_{pad}$  for impedance optimization. A table containing suggested values are shown in Table 1.

TEMPLATE FILENAME: AS1704602.DOC

| TEMPLATE FILENAME: AS1704602.0      |  |

|-------------------------------------|--|

| I EIVIFLATE FILENAIVIE. AST/04002.L |  |