# S1D13746 TV Out Mobile Graphics Engine

# **Hardware Functional Specification**

Document Number: X74B-A-001-02

Status: Revision 2.3 - EPSON CONFIDENTIAL

Issue Date: 2011/06/09

© SEIKO EPSON CORPORATION 2006 - 2011. All Rights Reserved.

Information in this document is subject to change without notice. You may download and use this document, but only for your own use in evaluating Seiko Epson/EPSON products. You may not modify the document. Epson Research and Development, Inc. disclaims any representation that the contents of this document are accurate or current. The Programs/Technologies described in this document may contain material protected under U.S. and/or International Patent laws.

EPSON is a registered trademark of Seiko Epson Corporation. All other Trademarks are the property of their respective owners

# **Table of Contents**

| 1 | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 1.1 Scope                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|   | 1.2 Abbreviations and Acronyms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|   | 1.3 S1D13746 TV-Out Mobile Graphics Engine Family                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2 | Operational Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|   | 2.1 TV Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|   | 2.1.1 Writing Window Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|   | 2.1.2 Scaling Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

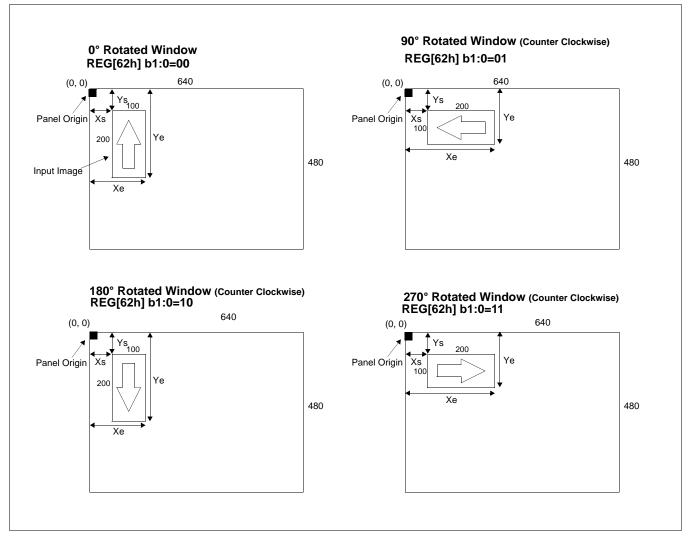

|   | 2.1.3 Window Rotation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|   | 2.1.4 Multiple TV Windows                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|   | 2.1.5 Single TV Window                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|   | 2.1.6 TV Window Border Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|   | 2.1.7 Double Buffered TV Window                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3 | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|   | 3.1 Integrated Display Buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|   | 3.2 CPU Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|   | 3.3 Input Data Formats                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|   | 3.4 TV Display Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|   | 3.5 TV Display Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|   | 3.6         Image Enhancement Engine         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         . </th |

|   | 3.7 Clock Source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|   | 3.8 Miscellaneous                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

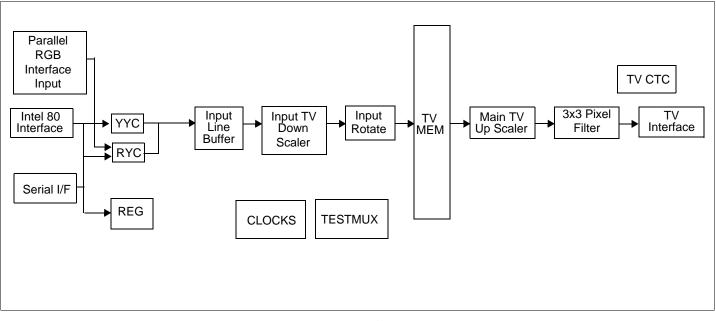

| 4 | Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

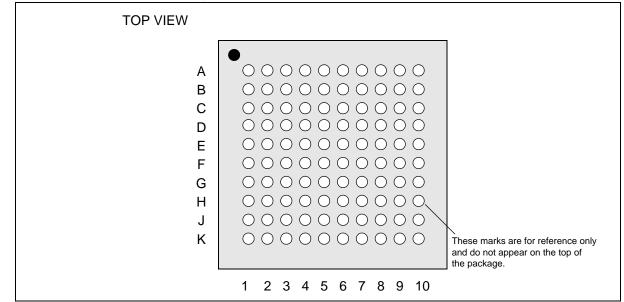

| 5 | Pinout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|   | 5.1 Package Pin Mapping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|   | 5.2 Pin Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|   | 5.2.1 Intel 80 Host Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|   | 5.2.2 Serial Peripheral Interface (SPI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|   | 5.2.3 TV Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|   | 5.2.4 Clocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|   | 5.2.5 Miscellaneous                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|   | 5.2.6 Power And Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|   | 5.3 Summary of Configuration Options                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 6 | Pin Mapping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|   | 6.1 Intel 80 Data Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|   | 6.2 Parallel RGB Data Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 7  | D.C. Characteristics                                         |

|----|--------------------------------------------------------------|

|    | 7.1 Absolute Maximum Ratings                                 |

|    | 7.2 Recommended Operating Conditions                         |

|    | 7.3 Electrical Characteristics                               |

|    | 7.4 DAC Characteristics                                      |

|    | 7.5 Power Estimation Guidelines                              |

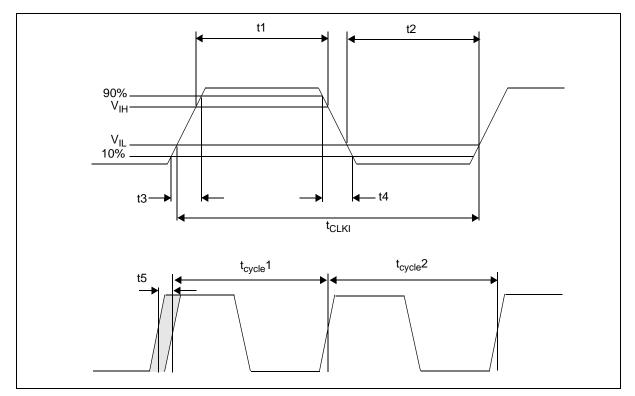

| 8  | A.C. Characteristics                                         |

|    | 8.1 Clock Timing                                             |

|    | 8.1.1 Input Clocks                                           |

|    | 8.1.2 OSC Clock                                              |

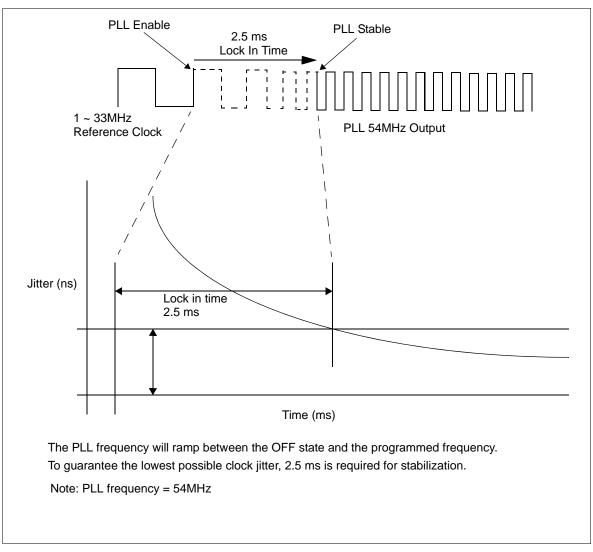

|    | 8.1.3 PLL Clock                                              |

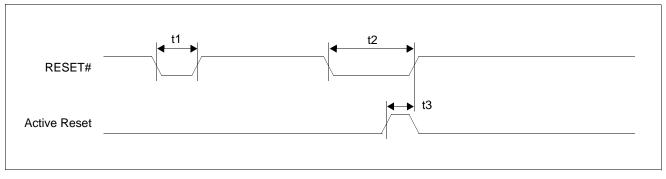

|    | 8.2 RESET# Timing                                            |

|    | 8.3 Host interface Timing                                    |

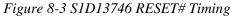

|    | 8.3.1 Intel 80 Interface Timing                              |

|    | 8.4 Serial Interface Timing                                  |

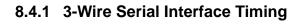

|    | 8.4.1 3-Wire Serial Interface Timing                         |

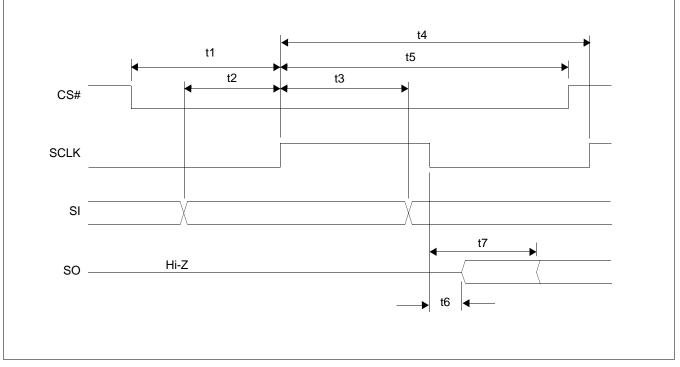

|    | 8.4.2 4-Wire Serial Interface (SPI) Timing                   |

|    | 8.5 Parallel RGB Interface Timing                            |

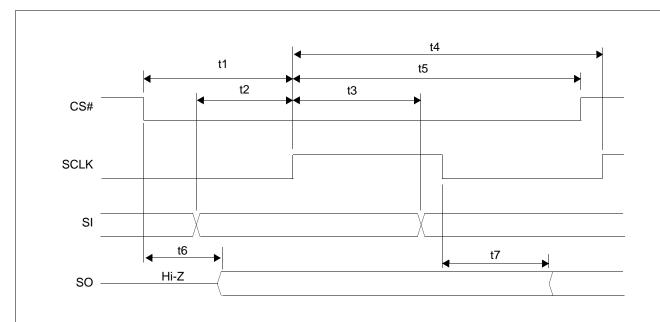

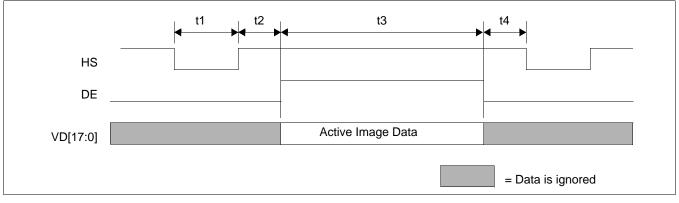

|    | 8.5.1 Vertical Timing                                        |

|    | 8.5.2 Horizontal Timing                                      |

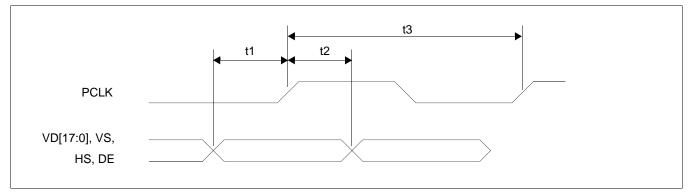

|    | 8.5.3 Input Signal Timings Relative to PCLK                  |

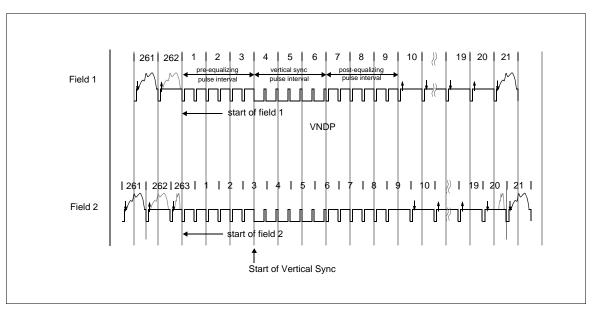

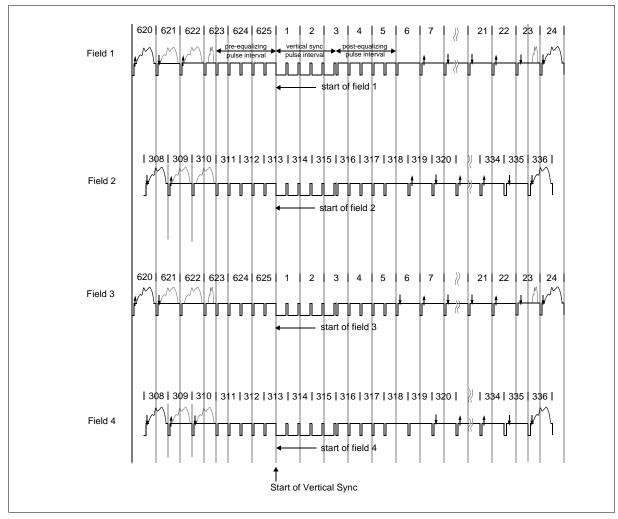

|    | 8.6 TV Timing                                                |

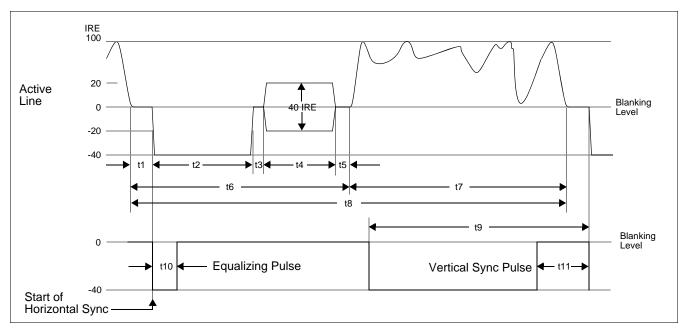

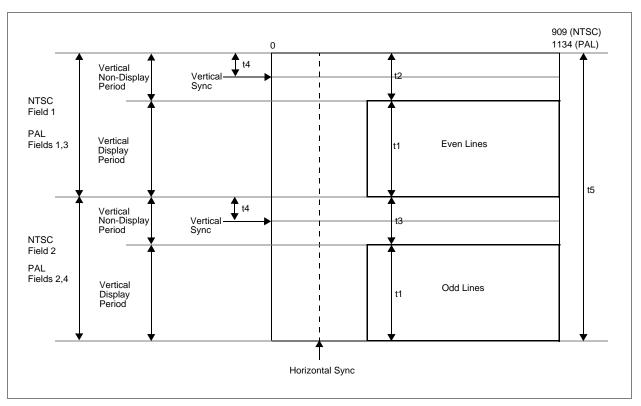

|    | 8.6.1 TV Output Timing                                       |

|    | 8.6.2 TV Output Parameters                                   |

| 9  | Clocks                                                       |

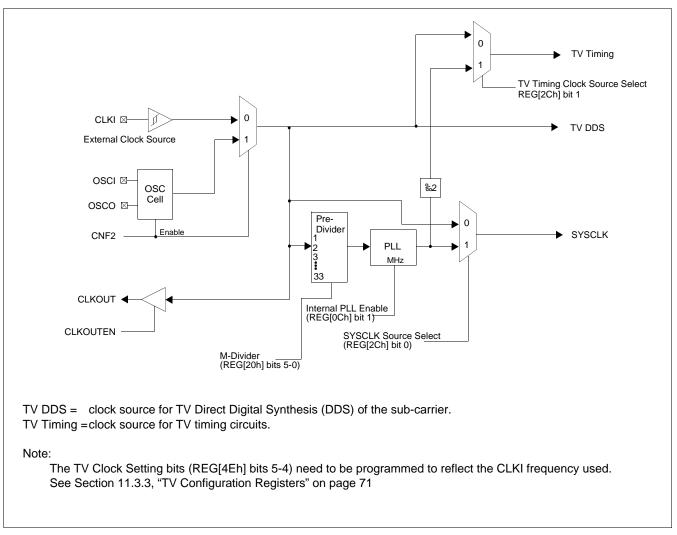

|    | 9.1 Clock Block Diagram                                      |

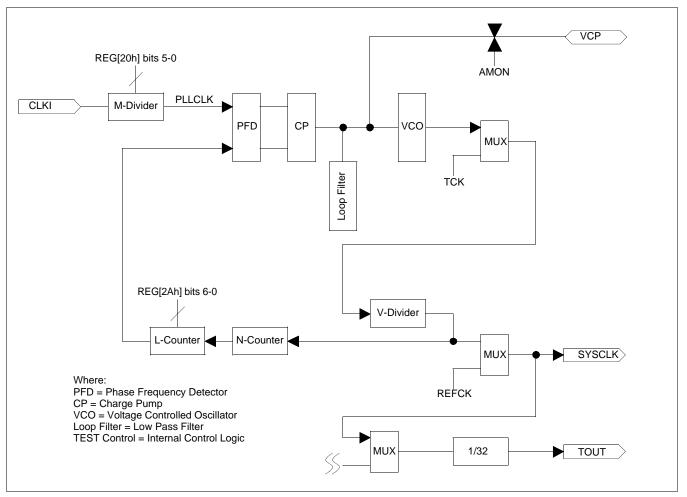

|    | 9.2 PLL Block Diagram                                        |

| 10 | Memory Map                                                   |

| 11 |                                                              |

| •• | 11.1 Register Mapping                                        |

|    | 11.2 Register Set                                            |

|    | 11.2 Register Descriptions                                   |

|    | 11.3.1 Product Information Registers       65                |

|    | 11.3.2 Clock Configuration Registers                         |

|    | 11.3.3 TV Configuration Registers                            |

|    | 11.3.4       Input Data Control Registers       86           |

|    | 11.3.5 Display Output Control Registers                      |

|    | 11.3.6 Display Memory Access Registers                       |

|    | 11.3.7    3X3 Pixel Matrix Filter Registers    11.3.7    103 |

| 11.3.8 Miscellaneous Registers                                                                                              | 114   |

|-----------------------------------------------------------------------------------------------------------------------------|-------|

| 11.3.9 General Purpose IO Pins Registers                                                                                    | 117   |

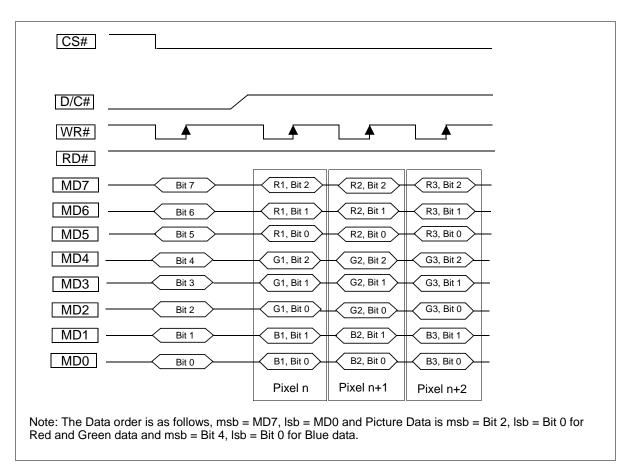

| 12 Intel 80, 8-Bit Interface Color Formats                                                                                  | . 119 |

| 12.1 8 bpp Mode (RGB 3:3:2), 256 colors                                                                                     | .119  |

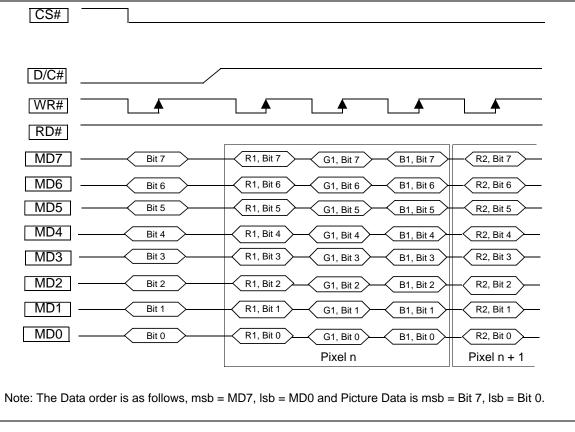

| 12.2 16 bpp Mode (RGB 5:6:5), 65,536 colors                                                                                 | .120  |

| 12.3 18 bpp (RGB 6:6:6), 262,144 colors                                                                                     | .121  |

| 12.4 24 bpp (RGB 8:8:8), 16,777,216 colors                                                                                  | .122  |

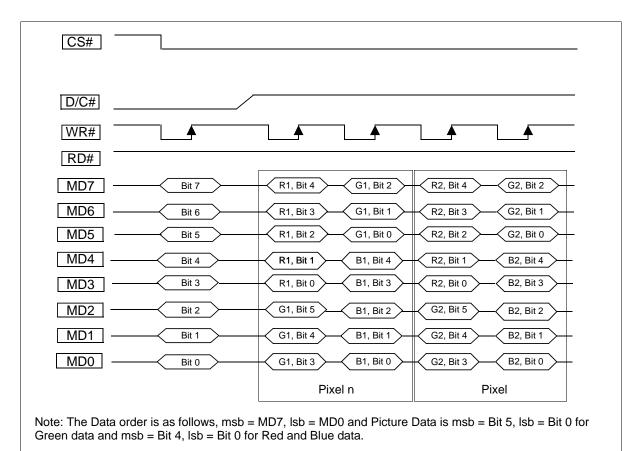

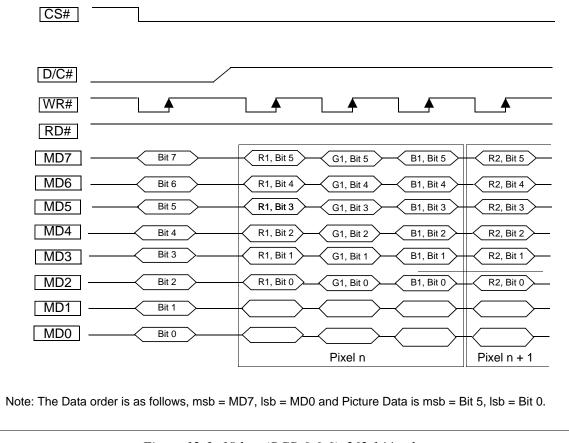

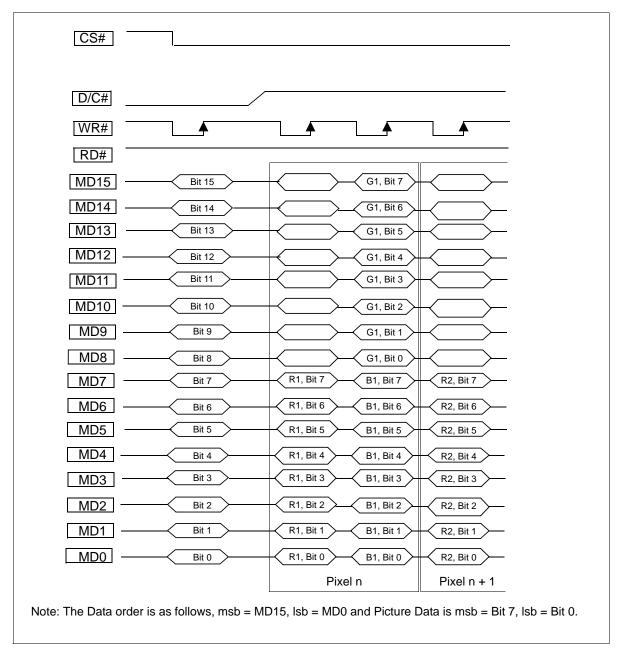

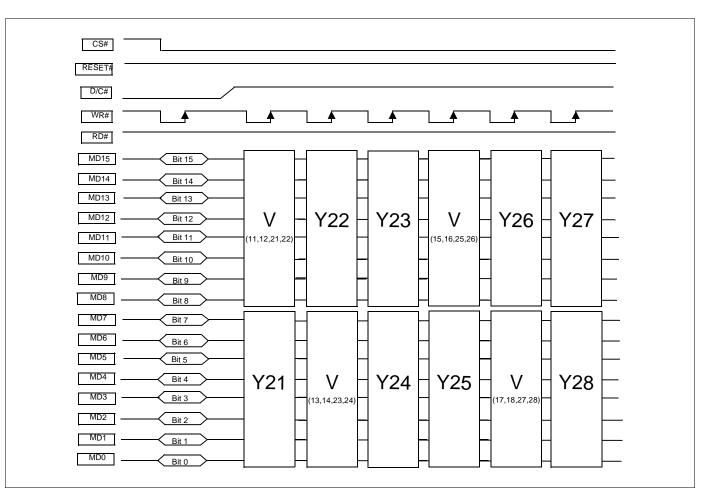

| 13 Intel 80, 16-bit Interface Color Formats                                                                                 | . 123 |

| 13.1 8 bpp (RGB 3:3:2), 256 colors                                                                                          | .123  |

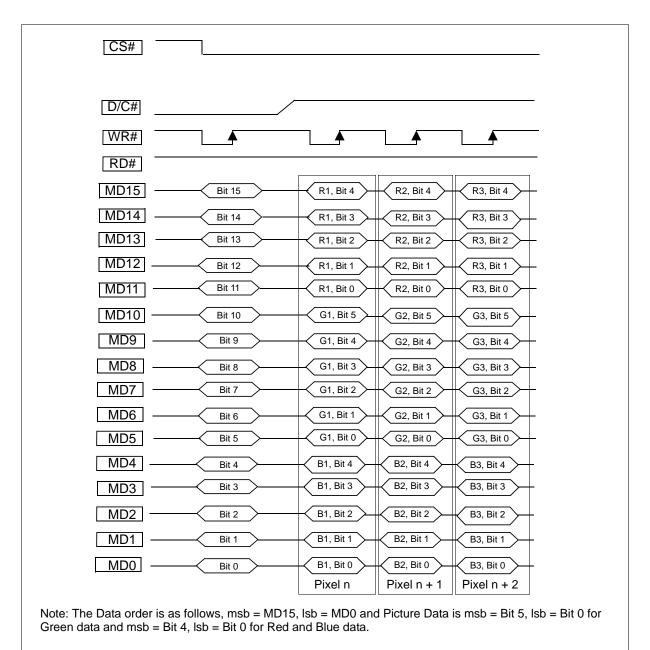

| 13.2 16 bpp (RGB 5:6:5), 65,536 colors                                                                                      | .124  |

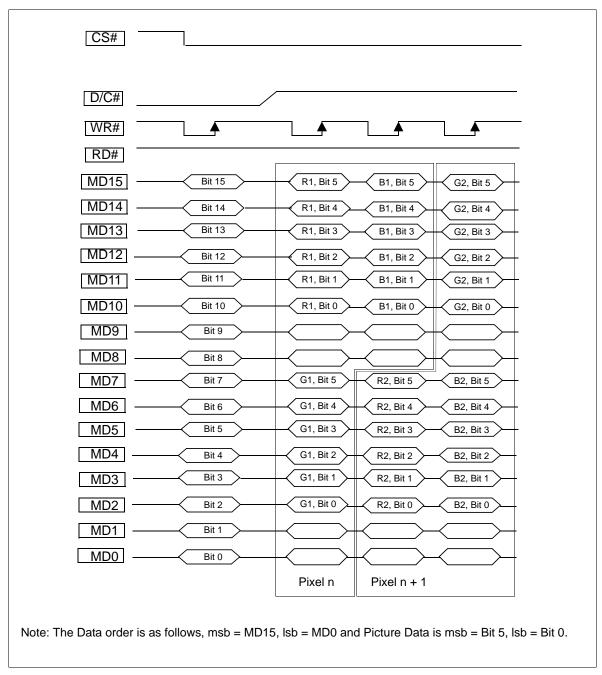

| 13.3 18 bpp Mode 1 (RGB 6:6:6), 262,144 colors                                                                              | .125  |

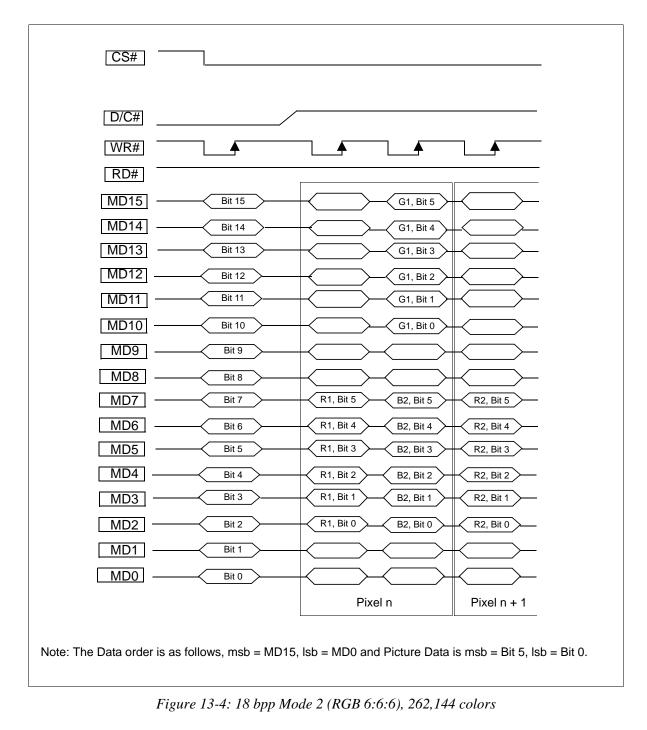

| 13.4 18 bpp Mode 2 (RGB 6:6:6), 262,144 colors                                                                              | .126  |

| 13.5 24 bpp Mode 1 (RGB 8:8:8), 16,777,216 colors                                                                           | .127  |

| 13.6 24 bpp Mode 2 (RGB 8:8:8), 16,777,216 colors                                                                           | .128  |

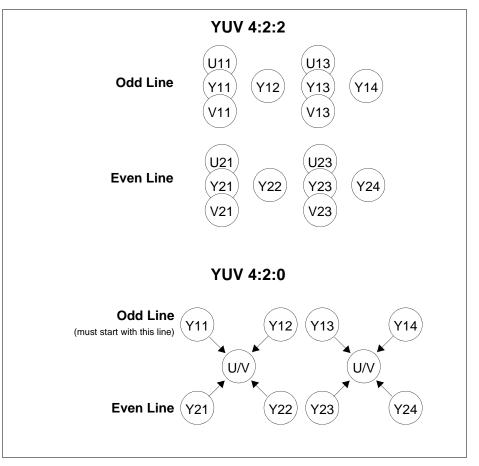

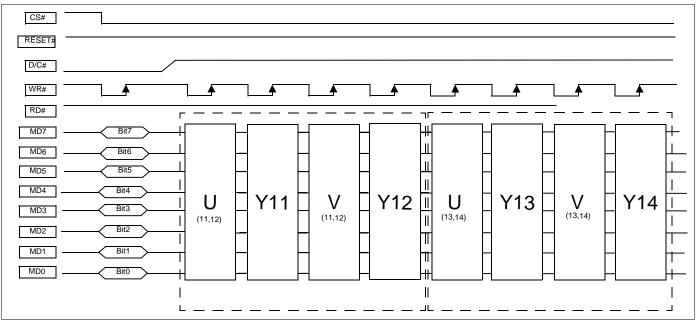

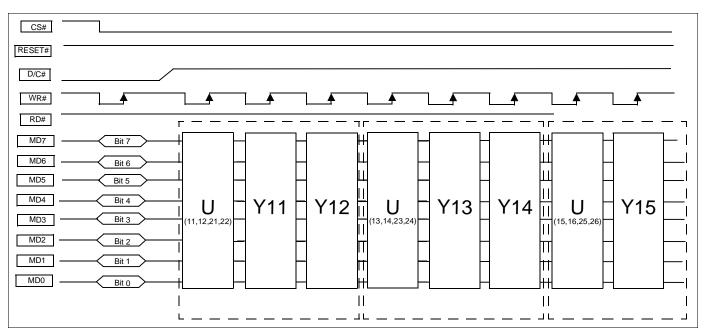

| 14 YUV Timing                                                                                                               | . 129 |

| 14.1 YUV 4:2:2 with Intel 80, 8-bit Interface                                                                               | .130  |

| 14.2 YUV 4:2:0 ODD Line with Intel 80, 8-bit Interface                                                                      | .130  |

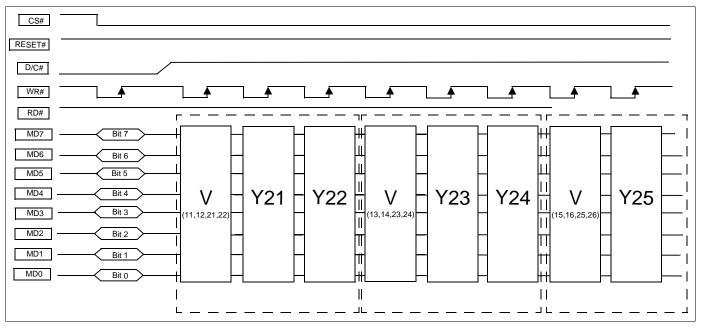

| 14.3 YUV 4:2:0 EVEN Line with Intel 80, 8-bit Interface                                                                     | .131  |

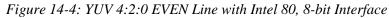

| 14.4 YUV 4:2:2 with Intel 80, 16-bit Interface                                                                              | .132  |

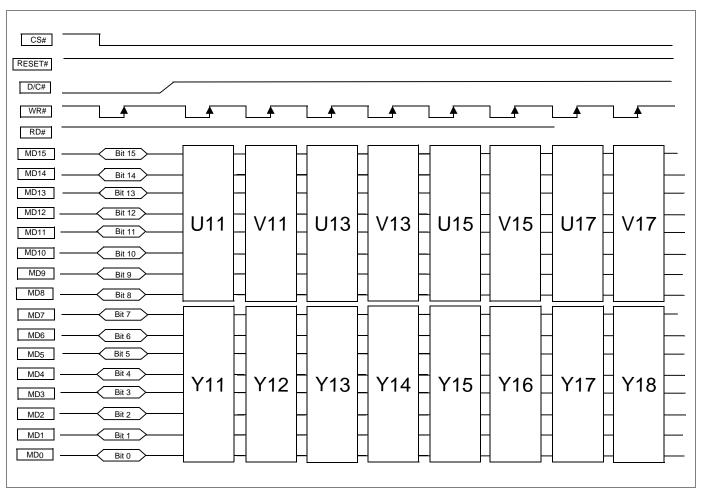

| 14.5 YUV 4:2:0 ODD Line with Intel 80, 16-bit Interface                                                                     | .133  |

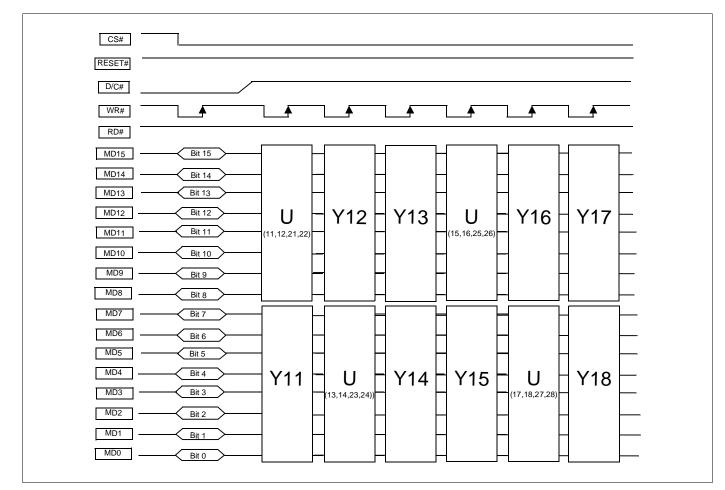

| 14.6 YUV 4:2:0 EVEN Line with Intel 80, 16-bit Interface                                                                    | .134  |

| 15 SwivelView™                                                                                                              | . 135 |

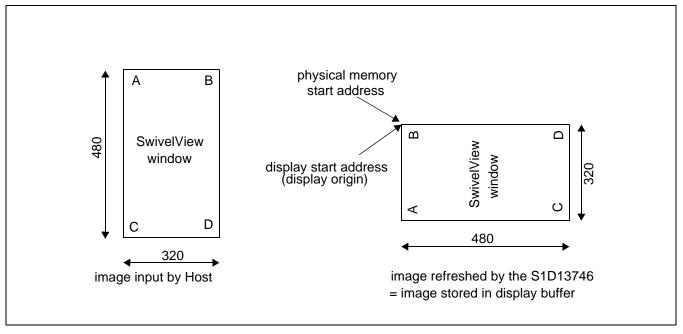

| 15.1 SwivelView <sup>TM</sup> Concept                                                                                       | . 135 |

| 15.2 90° SwivelView <sup>TM</sup> $\ldots$ | .136  |

| 15.2.1 Register Programming                                                                                                 | 136   |

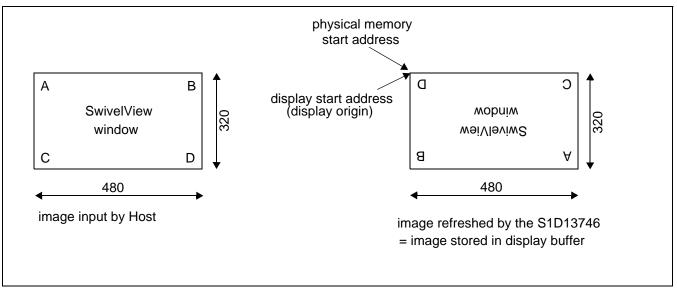

| 15.3 $180^{\circ}$ SwivelView <sup>TM</sup>                                                                                 | .137  |

| 15.3.1 Register Programming                                                                                                 | 137   |

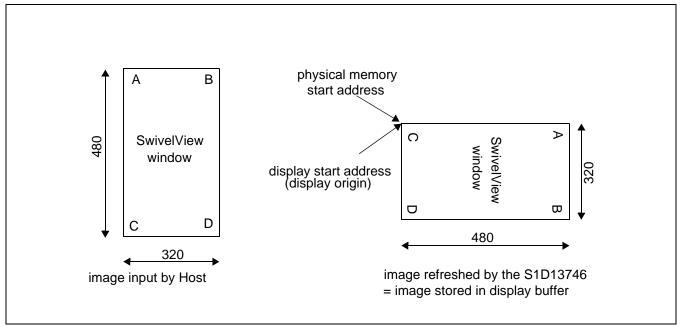

| 15.4 $270^{\circ}$ SwivelView <sup>TM</sup>                                                                                 | .138  |

| 15.4.1 Register Programming                                                                                                 | 138   |

| 15.5 Sub-Window Position / Rotation                                                                                         | . 139 |

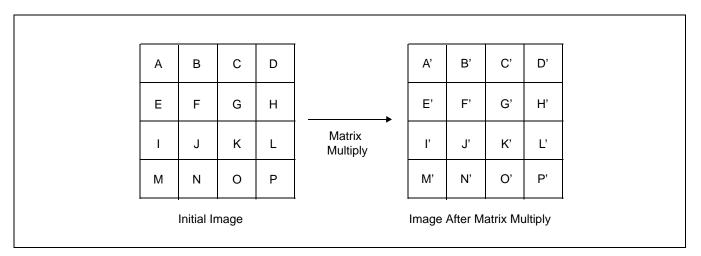

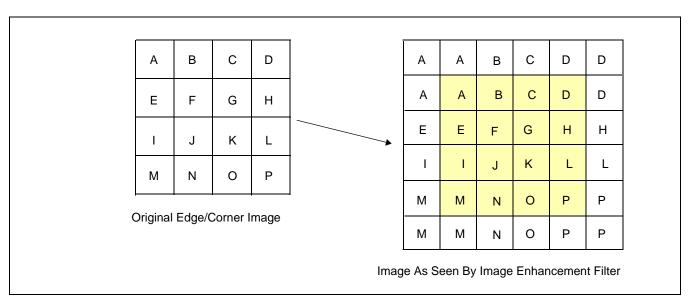

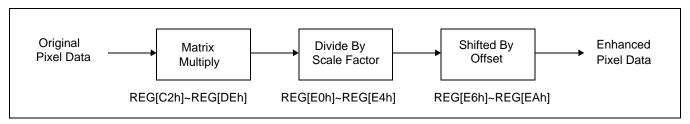

| 16 Image Enhancement Engine                                                                                                 | . 140 |

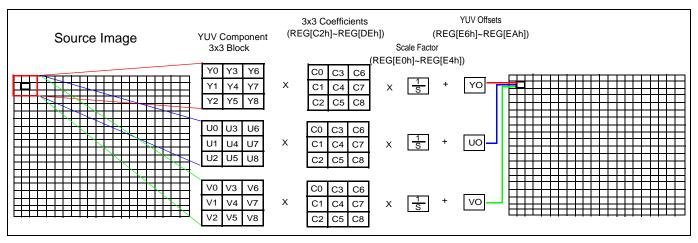

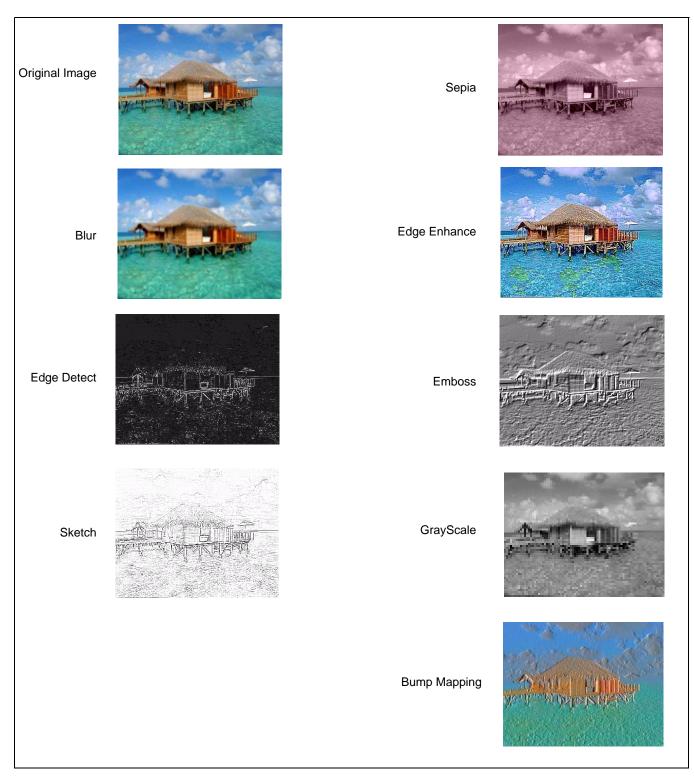

| 16.1 3x3 Filter                                                                                                             | . 140 |

| 16.1.1 Example Programming Values                                                                                           | 142   |

| 17 Host Interface                                                                                                           | . 143 |

| 17.1 Using the Intel 80 Interface                                                                                           |       |

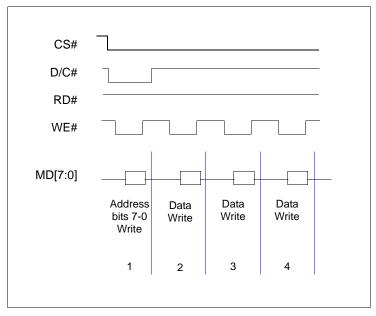

| 17.1.1 Register Write Procedure                                                                                             | 144   |

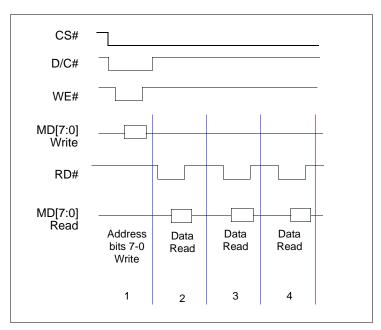

| 17.1.2 Register Read Procedure                                                                                              | 145   |

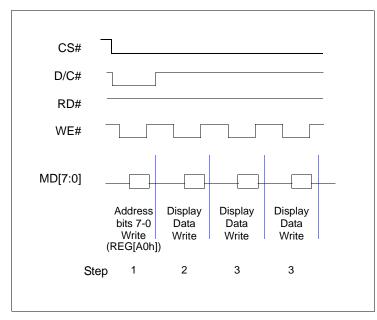

| 17.1.3 Sequential Memory Write Procedure                                                                                    | 146   |

| 17.2 Serial Host Interface                                                                                                  | . 147 |

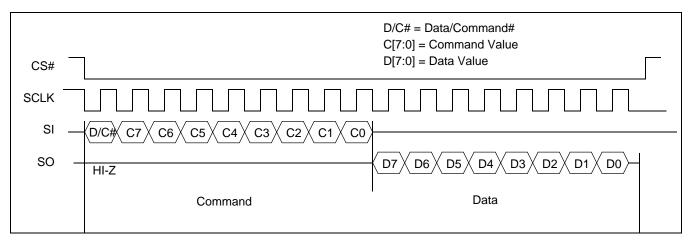

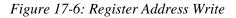

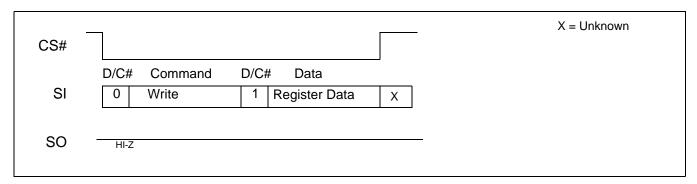

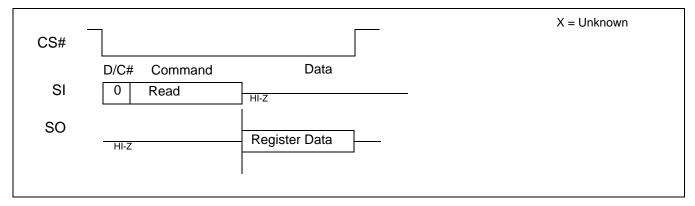

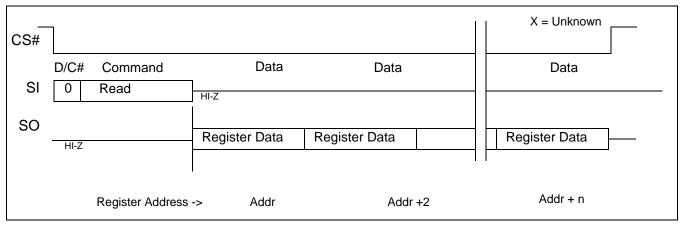

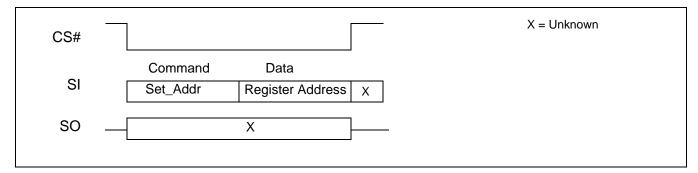

|                                  | 17.2.1 3 Wire 9-bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

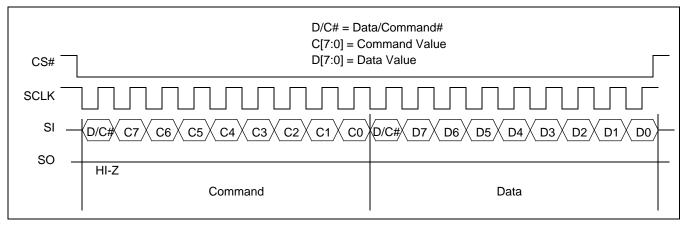

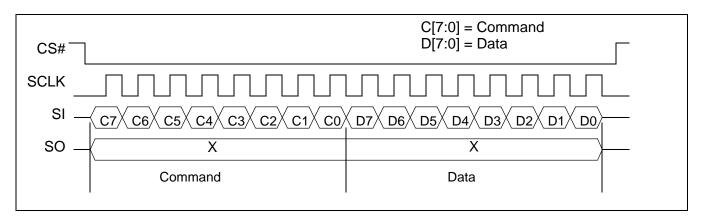

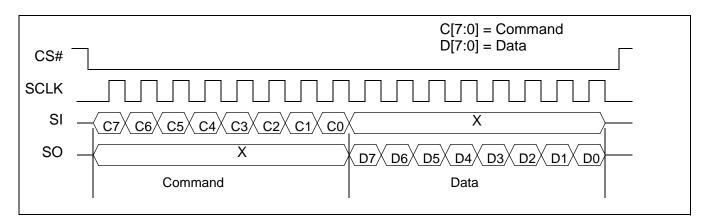

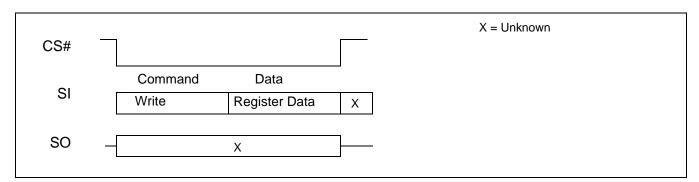

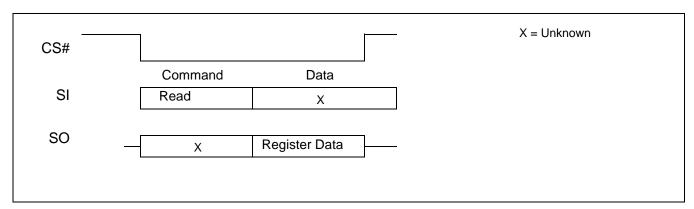

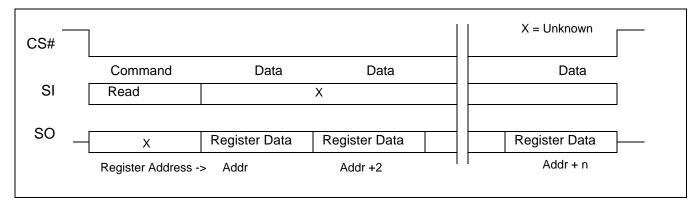

|                                  | 17.2.2 SPI Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 18                               | Parallel RGB Interface Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

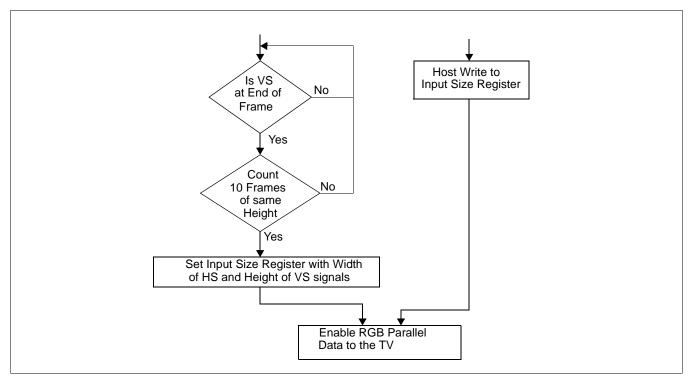

|                                  | 18.1 Width and Height Auto Detect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 19                               | VBI and Wide-Screen Signalling Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                  | 19.1 CEA-608-B Auto Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                  | 19.2 CEA-608-B Manual Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 20                               | Typical Use Case Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                  | 20.1 Initializing the S1D13746                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

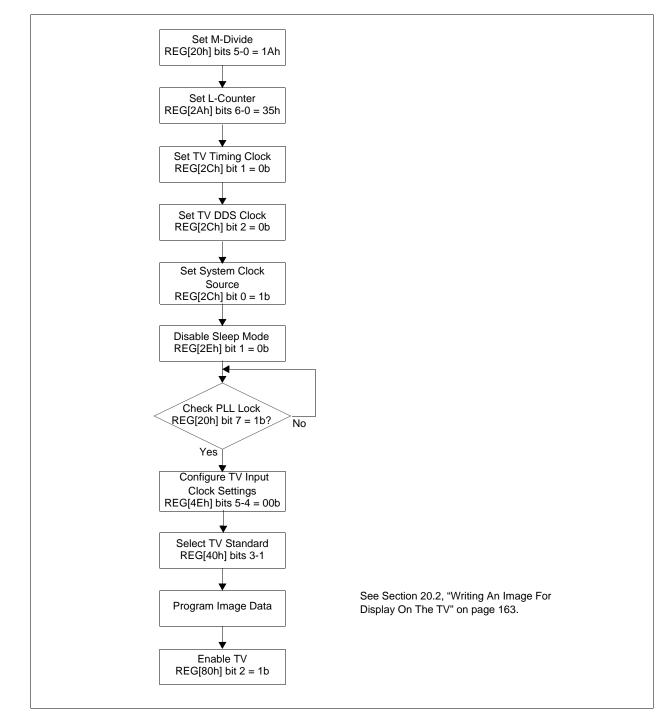

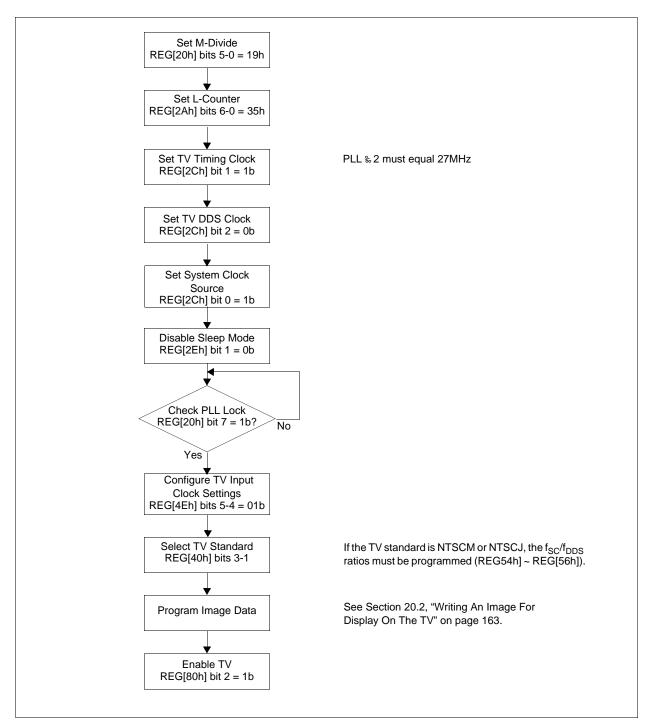

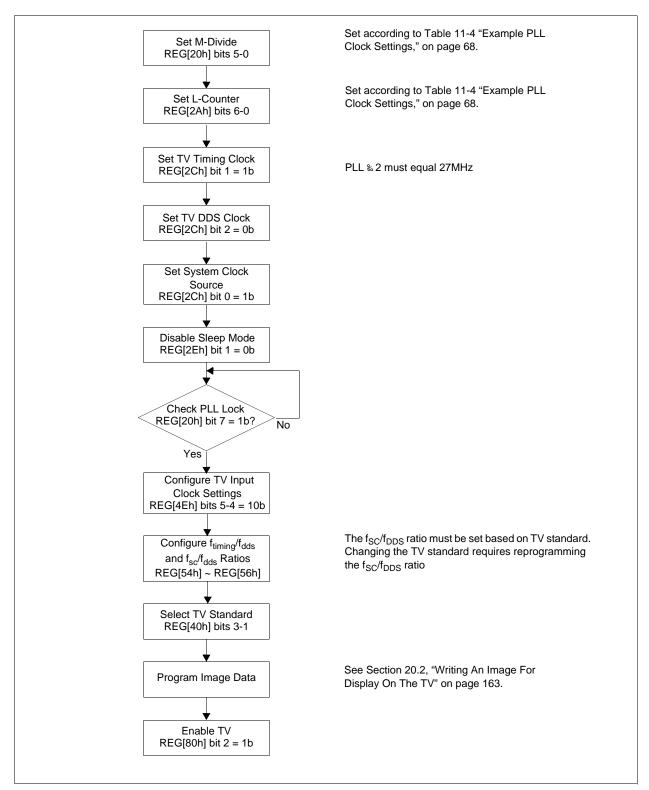

|                                  | 20.1.1 Initialization Flow Charts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                  | 20.2 Writing An Image For Display On The TV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                  | 20.3 Use Case Flowcharts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

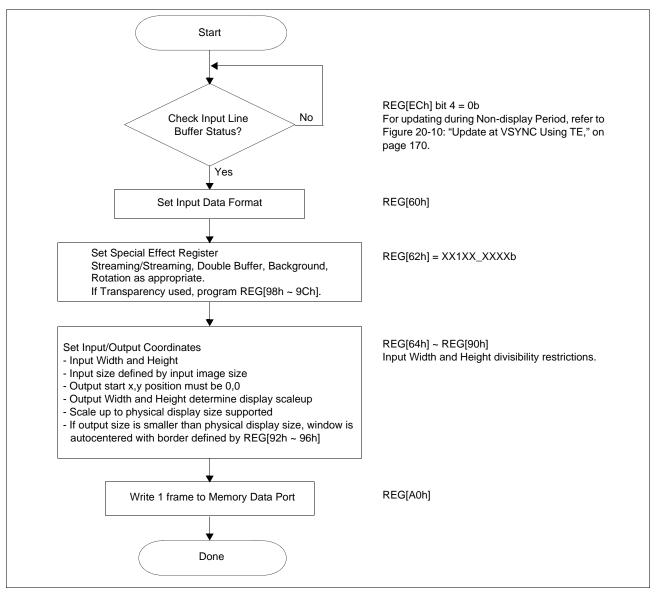

|                                  | 20.3.1 Host Write Background                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

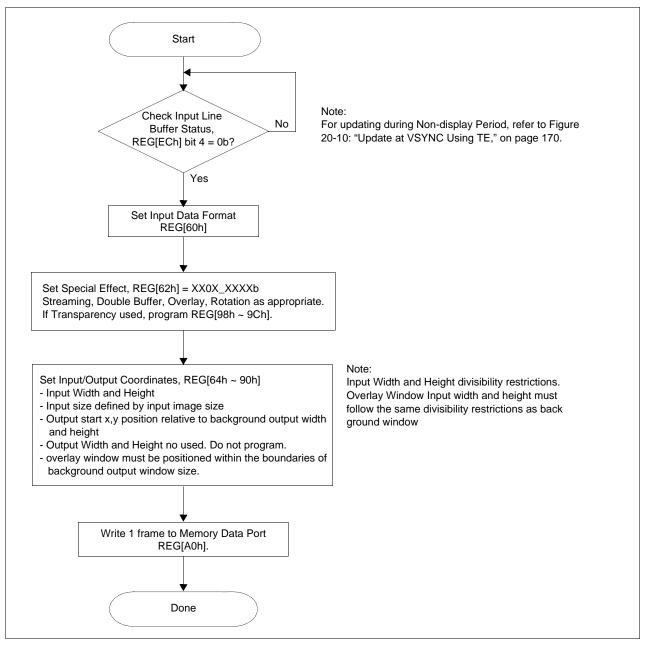

|                                  | 20.3.2 Host Write Overlay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

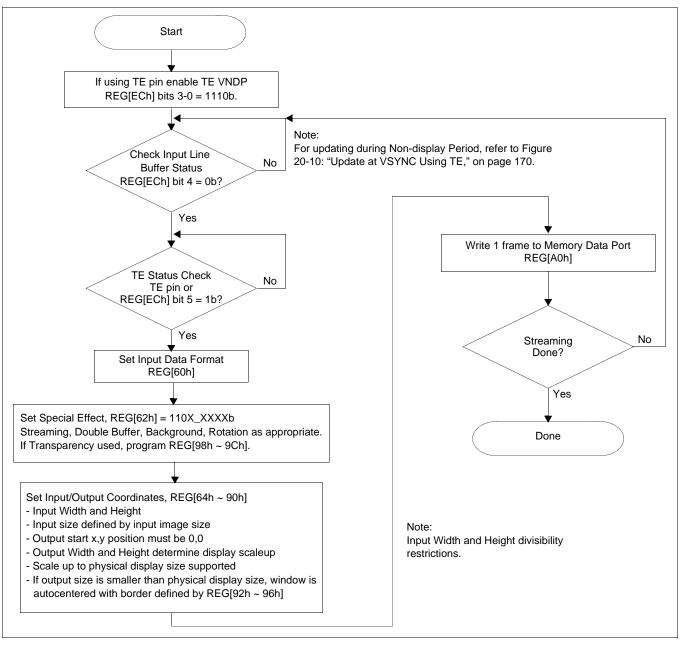

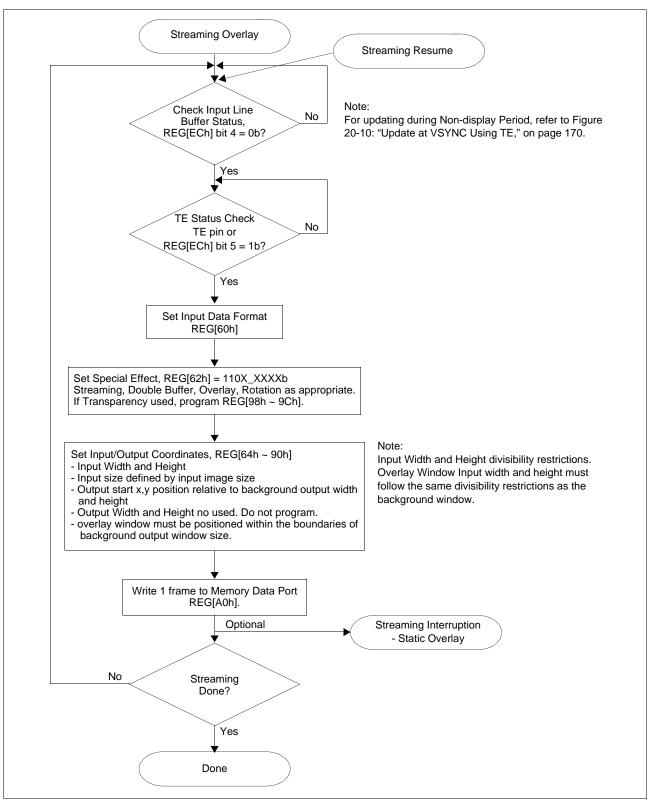

|                                  | 20.3.3 Streaming Background                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

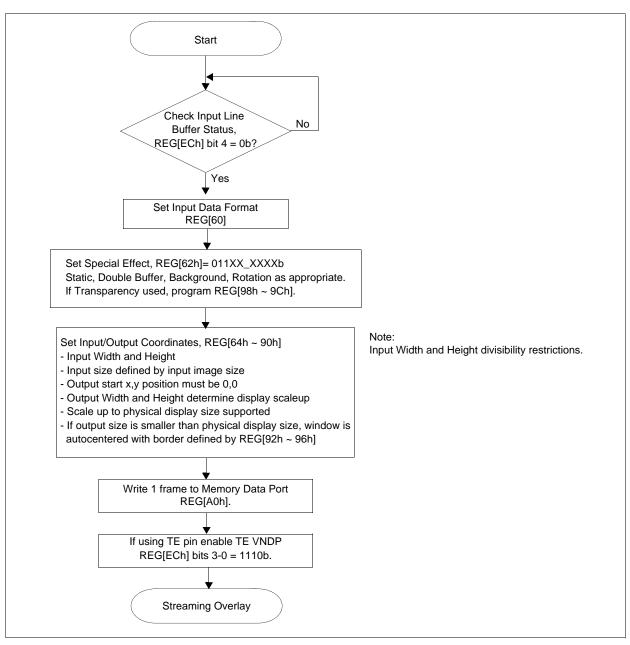

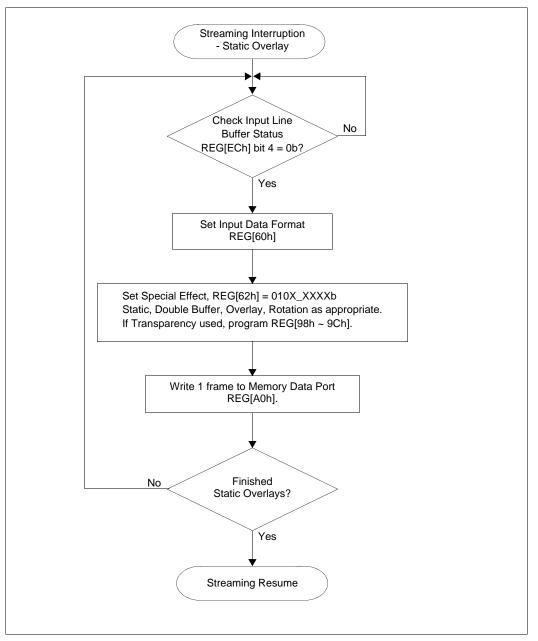

|                                  | 20.3.4 Background and Streaming Overlay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

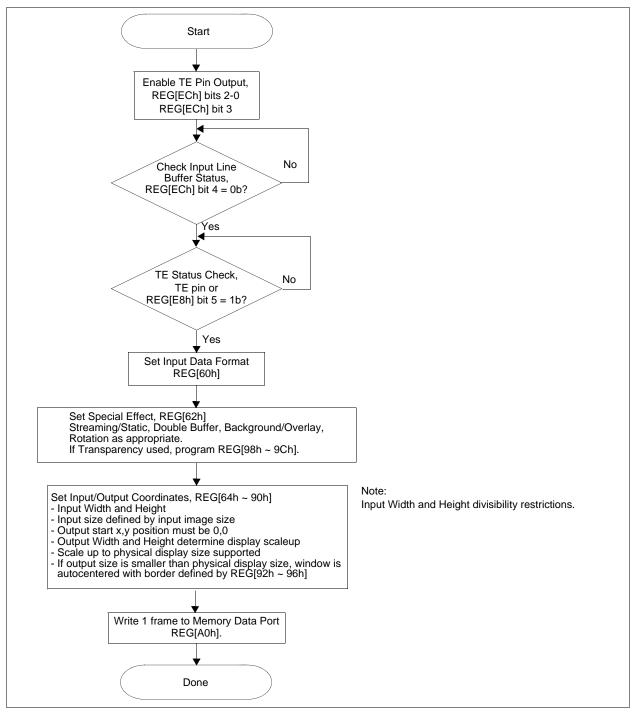

|                                  | 20.3.5 Update at VSYNC Using TE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

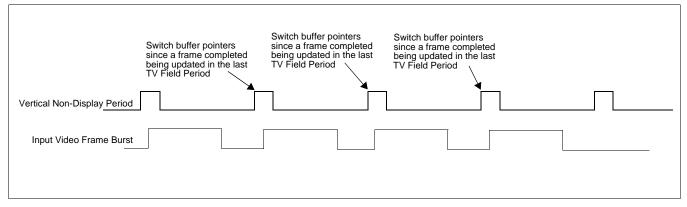

|                                  | 20.4 Example. Enable a Double-Burleted window on TV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| ~                                | Devide Deffer Description 470                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

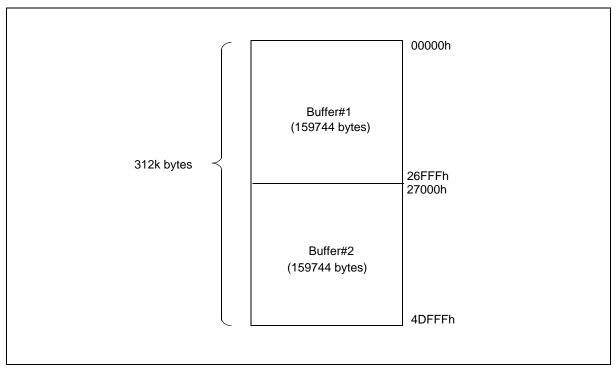

| 21                               | Double Buffer Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                  | 21.1 Double Buffering Limitations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                  | 21.1 Double Buffering Limitations    175      TV Filter Operation    176                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

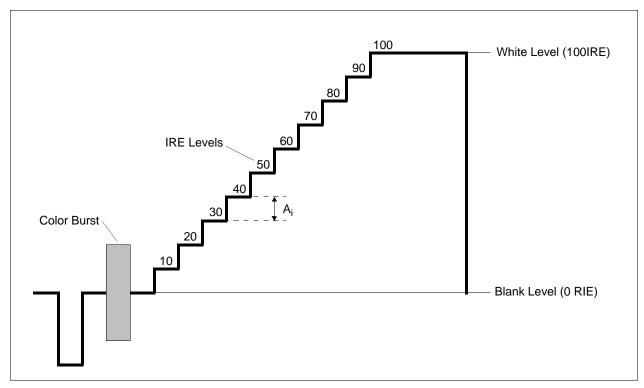

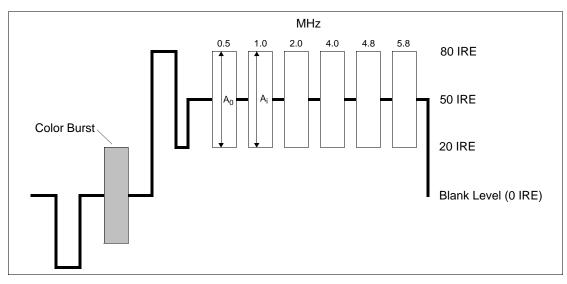

|                                  | 21.1 Double Buffering Limitations175 <b>TV Filter Operation176</b> 22.1 Generating Custom Luminance (Y) and Color (UV) Filter Coefficients176                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 22                               | 21.1 Double Buffering Limitations       175 <b>TV Filter Operation 176</b> 22.1 Generating Custom Luminance (Y) and Color (UV) Filter Coefficients       176         22.1.1 Filter Parameters       177                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 22                               | 21.1 Double Buffering Limitations       175 <b>TV Filter Operation 176</b> 22.1 Generating Custom Luminance (Y) and Color (UV) Filter Coefficients       176         22.1.1 Filter Parameters       177 <b>Power Save Modes</b> 180                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 22                               | 21.1 Double Buffering Limitations       175 <b>TV Filter Operation 176</b> 22.1 Generating Custom Luminance (Y) and Color (UV) Filter Coefficients       176         22.1.1 Filter Parameters       177 <b>Power Save Modes</b> 180         23.1 Sleep Mode       180                                                                                                                                                                                                                                                                                                                                                                                |

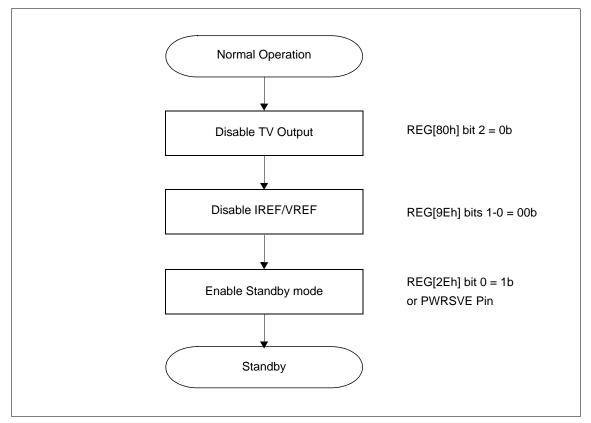

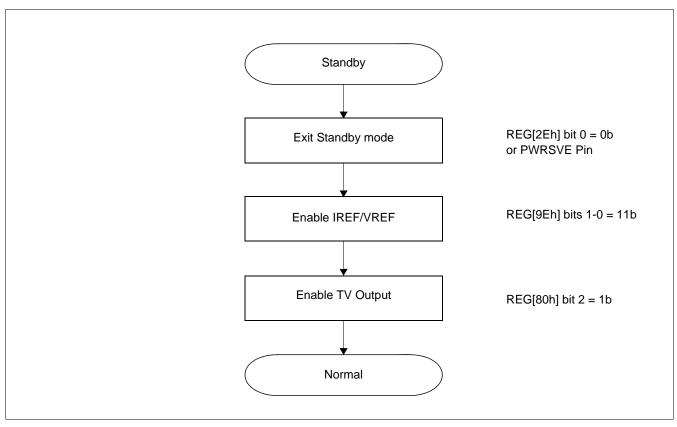

| 22<br>23                         | 21.1 Double Buffering Limitations       175         TV Filter Operation       176         22.1 Generating Custom Luminance (Y) and Color (UV) Filter Coefficients       176         22.1.1 Filter Parameters       177         Power Save Modes       180         23.1 Sleep Mode       180         23.2 Standby Mode       182                                                                                                                                                                                                                                                                                                                      |

| 22<br>23                         | 21.1 Double Buffering Limitations       175         TV Filter Operation       176         22.1 Generating Custom Luminance (Y) and Color (UV) Filter Coefficients       176         22.1.1 Filter Parameters       177         Power Save Modes       180         23.1 Sleep Mode       180         23.2 Standby Mode       182         External Components       184                                                                                                                                                                                                                                                                                |

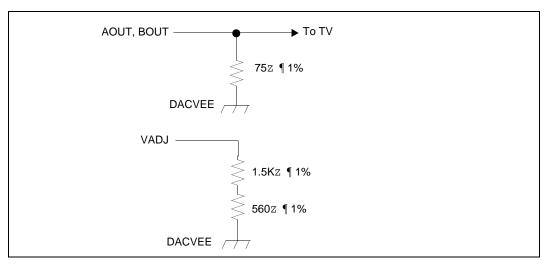

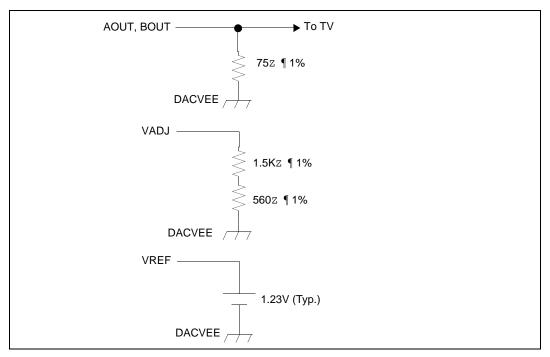

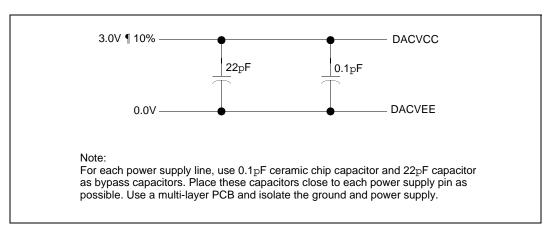

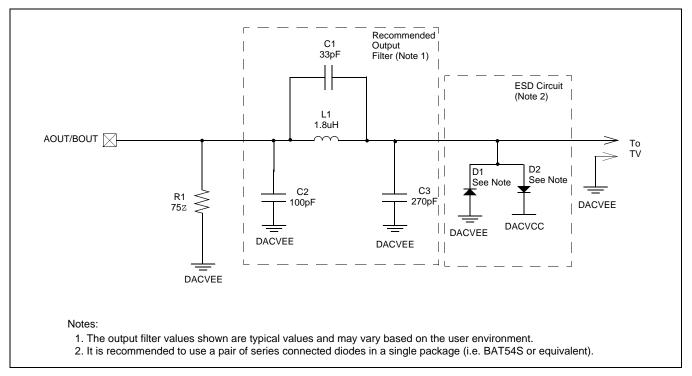

| 22<br>23                         | 21.1 Double Buffering Limitations175 <b>TV Filter Operation176</b> 22.1 Generating Custom Luminance (Y) and Color (UV) Filter Coefficients17622.1.1 Filter Parameters177 <b>Power Save Modes180</b> 23.1 Sleep Mode18023.2 Standby Mode182 <b>External Components184</b> 24.1 DAC External Components184                                                                                                                                                                                                                                                                                                                                             |

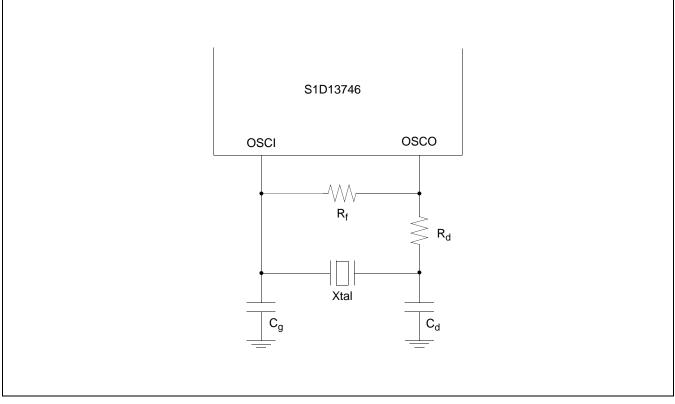

| 22<br>23<br>24                   | 21.1 Double Buffering Limitations       175         TV Filter Operation       176         22.1 Generating Custom Luminance (Y) and Color (UV) Filter Coefficients       176         22.1.1 Filter Parameters       177         Power Save Modes       180         23.1 Sleep Mode       180         23.2 Standby Mode       182         External Components       184         24.1 DAC External Components       184         24.2 Crystal Oscillator Circuit       186                                                                                                                                                                               |

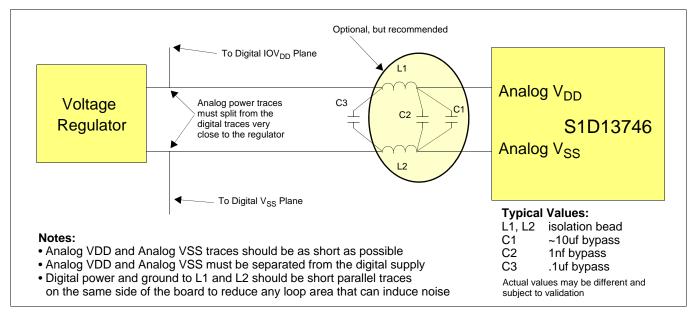

| 22<br>23<br>24                   | 21.1 Double Buffering Limitations175TV Filter Operation17622.1 Generating Custom Luminance (Y) and Color (UV) Filter Coefficients17622.1.1 Filter Parameters177Power Save Modes18023.1 Sleep Mode18023.2 Standby Mode182External Components18424.1 DAC External Components18424.2 Crystal Oscillator Circuit186Analog Power Supply Considerations187                                                                                                                                                                                                                                                                                                 |

| 22<br>23<br>24<br>25             | 21.1 Double Buffering Limitations175TV Filter Operation17622.1 Generating Custom Luminance (Y) and Color (UV) Filter Coefficients17622.1.1 Filter Parameters177Power Save Modes18023.1 Sleep Mode18023.2 Standby Mode182External Components18424.1 DAC External Components18424.2 Crystal Oscillator Circuit186Analog Power Supply Considerations18725.1 Guidelines for Analog Power Layout187                                                                                                                                                                                                                                                       |

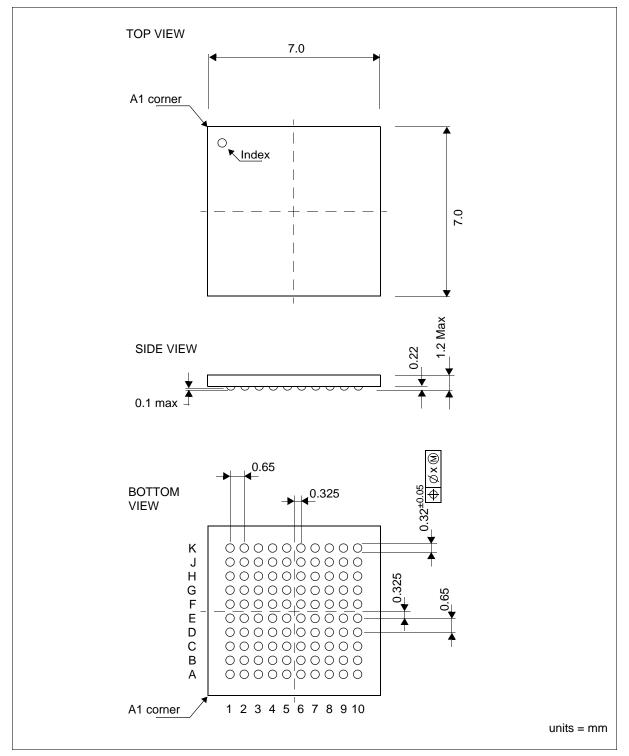

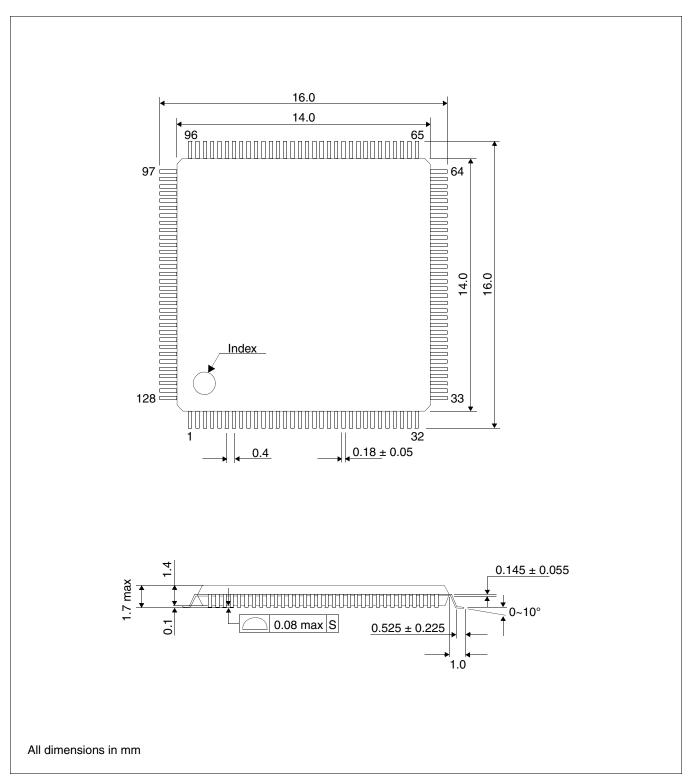

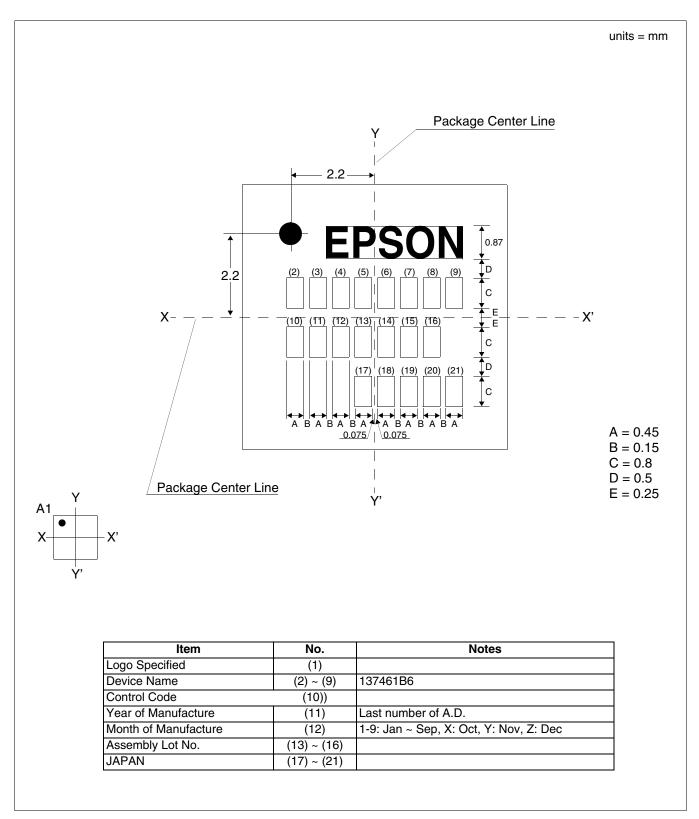

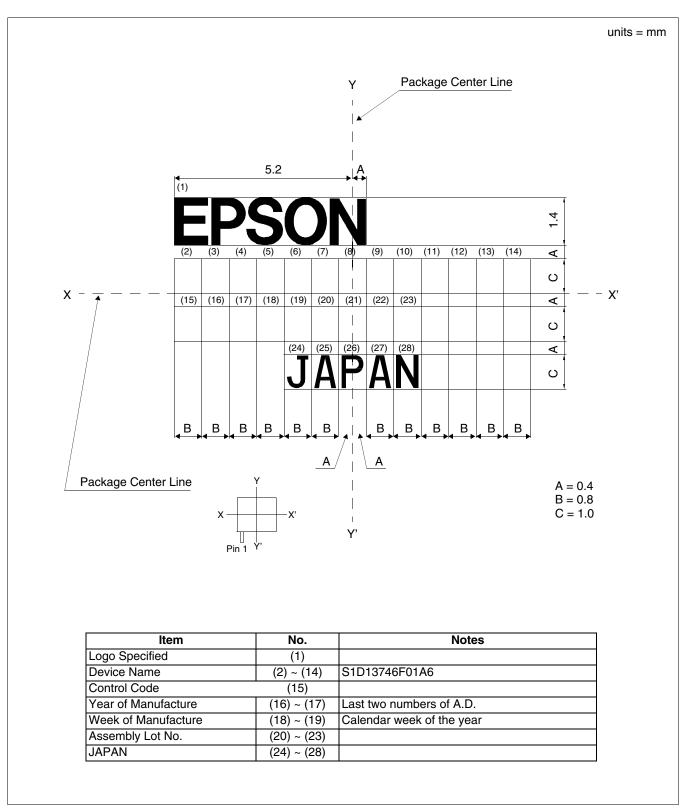

| 22<br>23<br>24<br>25<br>26       | 21.1 Double Buffering Limitations175TV Filter Operation17622.1 Generating Custom Luminance (Y) and Color (UV) Filter Coefficients17622.1.1 Filter Parameters177Power Save Modes18023.1 Sleep Mode18023.2 Standby Mode182External Components18424.1 DAC External Components18424.2 Crystal Oscillator Circuit186Analog Power Supply Considerations18725.1 Guidelines for Analog Power Layout187Mechanical Data189                                                                                                                                                                                                                                     |

| 22<br>23<br>24<br>25<br>26<br>27 | 21.1 Double Buffering Limitations       175         TV Filter Operation       176         22.1 Generating Custom Luminance (Y) and Color (UV) Filter Coefficients       176         22.1.1 Filter Parameters       177         Power Save Modes       180         23.1 Sleep Mode       180         23.2 Standby Mode       182         External Components       184         24.1 DAC External Components       184         24.2 Crystal Oscillator Circuit       186         Analog Power Supply Considerations       187         25.1 Guidelines for Analog Power Layout       187         Mechanical Data       189         References       194 |

| 22<br>23<br>24<br>25<br>26<br>27 | 21.1 Double Buffering Limitations175TV Filter Operation17622.1 Generating Custom Luminance (Y) and Color (UV) Filter Coefficients17622.1.1 Filter Parameters177Power Save Modes18023.1 Sleep Mode18023.2 Standby Mode182External Components18424.1 DAC External Components18424.2 Crystal Oscillator Circuit186Analog Power Supply Considerations18725.1 Guidelines for Analog Power Layout187Mechanical Data189                                                                                                                                                                                                                                     |

# 1 Introduction

# 1.1 Scope

This is the Hardware Functional Specification for the S1D13746, TV-Out Embedded Memory Mobile Graphics Engine. Included in this document are timing diagrams, AC and DC characteristics, register descriptions, and power management descriptions. This document is intended for two audiences: Video Subsystem Designers and Software Developers.

This document is updated as appropriate. Please check the Epson Research and Development Website at **www.erd.epson.com** for the latest revision of this document before beginning any development.

We appreciate your comments on our documentation. Please contact us via email at documentation@erd.epson.com.

## **1.2 Abbreviations and Acronyms**

The following abbreviations and acronyms are used in this document:

All numbers are in decimal unless marked otherwise (b for binary, h for hexadecimal)  $k = 2^{10} = 1024$  when used with regards to memory b = bitB = Bytebpp = bits-per-pixel msb = Most Significant bit lsb = Least Significant bit IO = Input/Output LUT = Look-Up Table NC = No ConnectionYYC = YUV to YUV Converter YRC = YUV to RGB Converter RYC = RGB to YUV Converter VDP = Vertical Display Period VNDP = Vertical Non-display Period DDS = Digital Direct Synthesis POUT = PLL Output

# 1.3 S1D13746 TV-Out Mobile Graphics Engine Family

The S1D13746 TV-Out Mobile Graphics Engine family currently includes the S1D13746B00 and the S1D13746B01/S1D13746F01. The following table describes the differences between these devices.

| Device      | Feature Differences                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

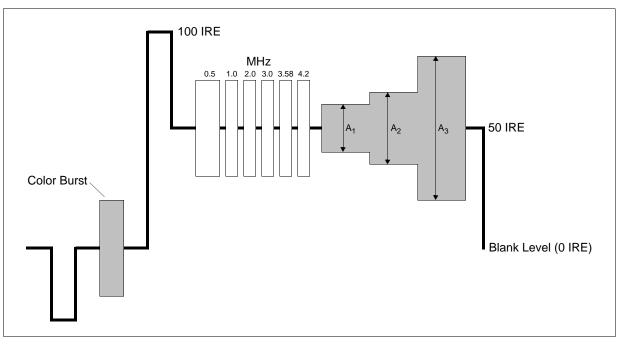

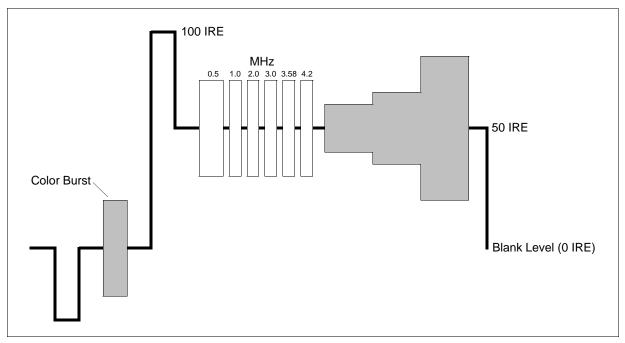

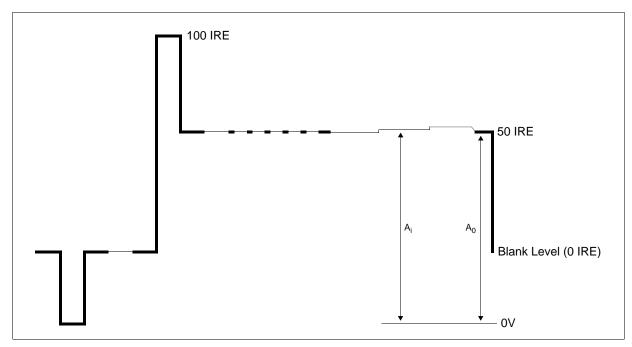

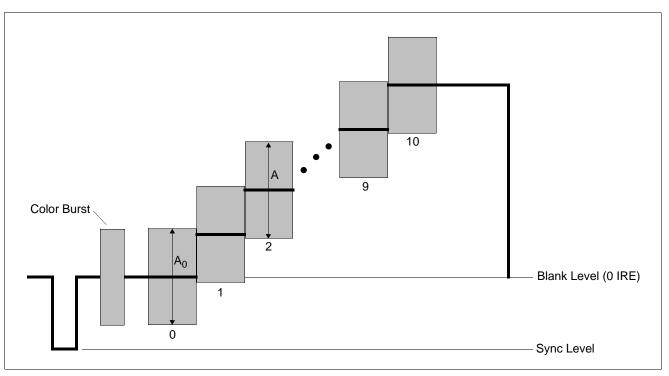

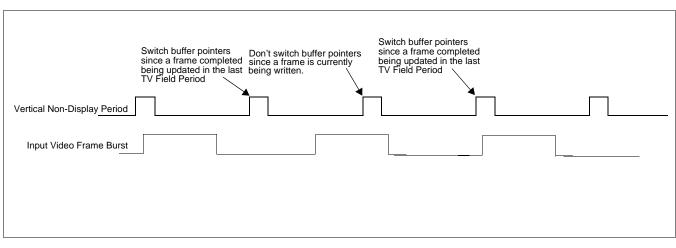

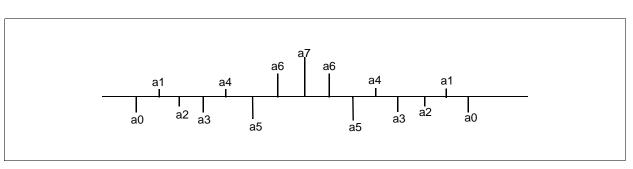

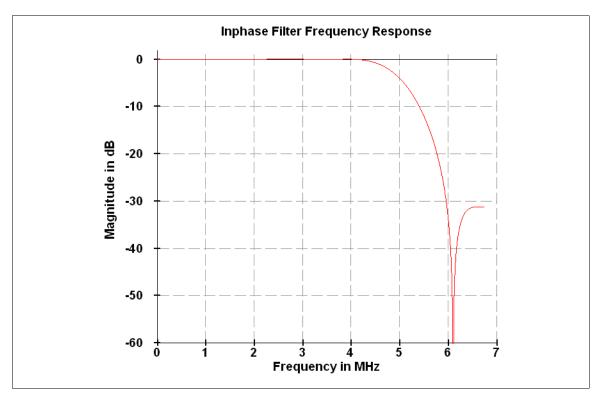

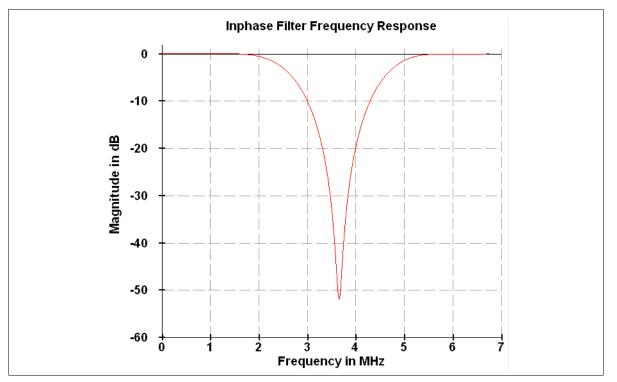

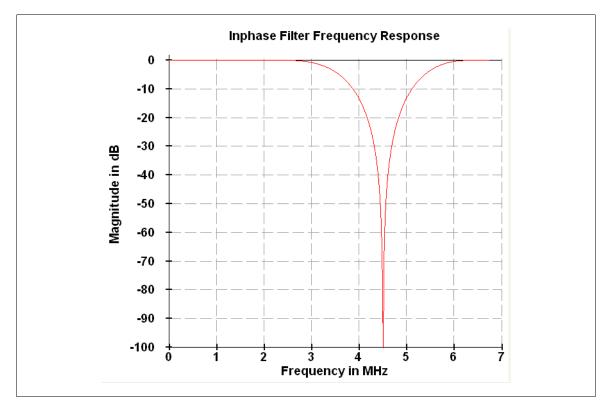

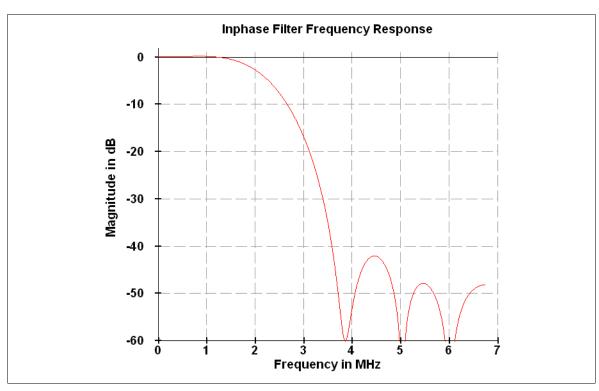

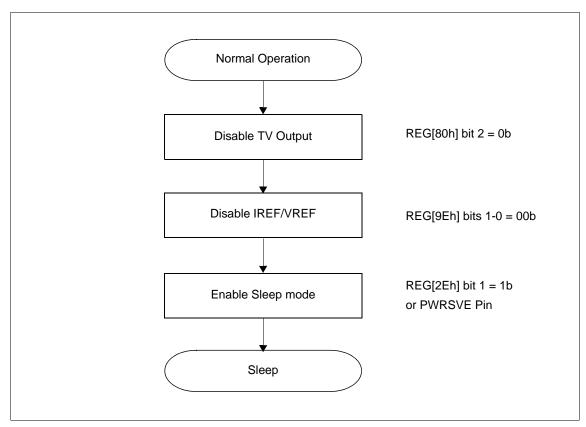

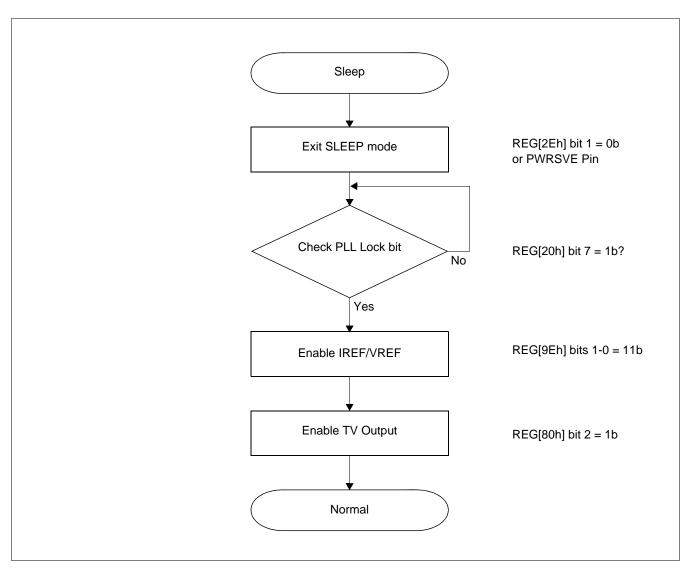

| S1D13746B00 | Base Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |