# Si7050/3/4/5-A20

## I<sup>2</sup>C TEMPERATURE SENSORS

#### Features

- High Accuracy Temperature Sensors

- Si7053: ±0.3 °C (max)

- Si7054: ±0.4 °C (max)

- Si7055: ±0.5 °C (max)

- Si7050: ±1.0 °C (max)

- Wide operating voltage (1.9 to 3.6 V)

- -40 to +125 °C operating range

- Accuracy maintained over the entire operating temperature and voltage range

- Low Power Consumption

- 195 nA average current @ 1 Hz sample rate

- 14-bit resolution

- Factory calibrated

- I<sup>2</sup>C interface

- 3x3 mm DFN package

#### Applications

- HVAC/R

- Thermostats

- White goods

- Computer equipment

- Portable consumer devices

- Asset tracking

- Cold chain storage

- Battery protection

- Industrial controls

- Medical equipment

#### Description

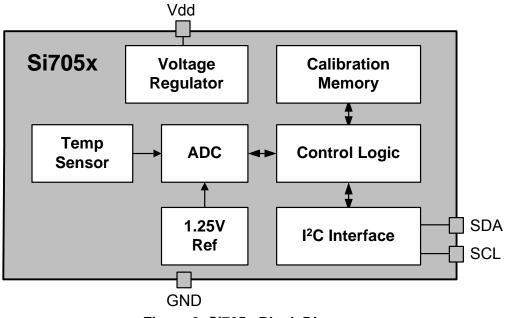

The Si705x Digital Temperature Sensors offer industry-leading low power consumption and high accuracy across the entire operating voltage and temperature range. These monolithic CMOS ICs feature a band-gap temperature sensor element, an analog-to-digital converter with up to 14-bit resolution, signal processing, calibration data, and an I<sup>2</sup>C interface. The patented use of novel signal processing and analog design enables the sensors to maintain their accuracy over a wide temperature and voltage range, while consuming very little current.

The temperature sensors are factory-calibrated and the calibration data is stored in the on-chip non-volatile memory. This ensures that the sensors are fully interchangeable, with no recalibration or software changes required.

The Si705x devices are available in a 3x3 mm DFN package, and the industry-standard I<sup>2</sup>C interface can operate at up to 400 kHz. Requiring just 195 nA of average current when sampled once per second, the Si705x can operate for several years with just a single coin cell battery.

The Si705x devices offer an accurate, low-power, factory-calibrated digital solution ideal for measuring temperature in applications ranging from HVAC/R and asset tracking to industrial and consumer platforms.

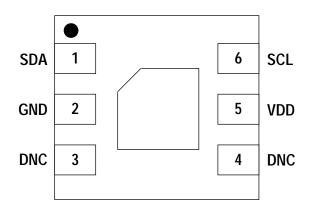

Top View SDA 1 6 SCL GND 2 5 VDD DNC 3 4 DNC

**Pin Assignments**

Patent Protected. Patents pending

## Si7050/3/4/5-A20

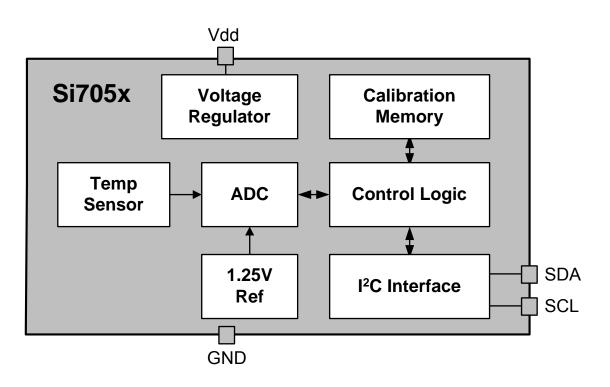

#### **Functional Block Diagram**

## TABLE OF CONTENTS

## Section

### <u>Page</u>

| 1. Electrical Specifications                |     |

|---------------------------------------------|-----|

| 2. Typical Application Circuits             |     |

| 3. Bill of Materials                        |     |

| 4. Functional Description                   |     |

| 5. I2C Interface                            |     |

| 5.1. Issuing a Measurement Command          | .13 |

| 5.2. Reading and Writing User Registers     | .14 |

| 5.3. Electronic Serial Number               | .15 |

| 5.4. Firmware Revision                      | .16 |

| 6. Control Registers                        |     |

| 6.1. Register Descriptions                  |     |

| 7. Pin Descriptions: Si705x (Top View)      |     |

| 8. Ordering Guide                           |     |

| 9. Package Outline                          | .20 |

| 9.1. Package Outline: 3x3 6-pin DFN         |     |

| 10. PCB Land Pattern and Solder Mask Design |     |

| 11. Top Marking                             |     |

| 11.1. Si705x Top Marking                    |     |

| 11.2. Top Marking Explanation               |     |

| 12. Additional Reference Resources          |     |

| Document Change List                        | .25 |

| Contact Information                         |     |

### **1. Electrical Specifications**

Unless otherwise specified, all min/max specifications apply over the recommended operating conditions.

#### **Table 1. Recommended Operating Conditions**

| Parameter             | Symbol | Test Condition | Min | Тур | Max  | Unit |

|-----------------------|--------|----------------|-----|-----|------|------|

| Power Supply          | Vdd    |                | 1.9 | —   | 3.6  | V    |

| Operating Temperature | TA     |                | -40 |     | +125 | °C   |

#### **Table 2. General Specifications**

$1.9 \le V_{DD} \le 3.6$  V; TA = -40 to 125 °C default conversion time unless otherwise noted.

| Parameter           | Symbol            | Test Condition                                                        | Min       | Тур  | Max       | Unit |

|---------------------|-------------------|-----------------------------------------------------------------------|-----------|------|-----------|------|

| Input Voltage High  | V <sub>IH</sub>   | SCL, SDA pins                                                         | 0.7 x Vdd |      |           | V    |

| Input Voltage Low   | VIL               | SCL, SDA pins                                                         |           |      | 0.3 x Vdd | V    |

| Input Voltage Range | Vin               | SCL, SDA pins with respect to GND                                     | 0.0       |      | Vdd       | V    |

| Input Leakage       | lı∟               | SCL, SDA pins                                                         |           |      | 1         | μA   |

| Output Voltage Low  | Vol               | SDA pin; IOL = 2.5 mA; VDD = 3.3 V                                    |           |      | 0.6       | V    |

|                     |                   | SDA pin; IoL = 1.2 mA;<br>VDD = 1.9 V                                 | —         | —    | 0.4       | V    |

| Current             | IDD               | Temperature conversion in progress                                    |           | 90   | 120       | μA   |

| Consumption         |                   | Standby, –40 to +85 °C <sup>1</sup>                                   |           | 0.06 | 0.62      | μA   |

|                     |                   | Standby, –40 to +125 °C <sup>1</sup>                                  |           | 0.06 | 3.8       | μA   |

|                     |                   | Peak IDD during powerup <sup>2</sup>                                  |           | 3.5  | 4.0       | mA   |

|                     |                   | Peak IDD during I <sup>2</sup> C operations <sup>3</sup>              |           | 3.5  | 4.0       | mA   |

| Conversion Time     | t <sub>CONV</sub> | 14-bit temperature                                                    | _         | 7    | 10.8      | ms   |

|                     | -                 | 13-bit temperature                                                    |           | 4    | 6.2       | ms   |

|                     |                   | 12-bit temperature                                                    |           | 2.4  | 3.8       | ms   |

|                     | -                 | 11-bit temperature                                                    |           | 1.5  | 2.4       | ms   |

| Powerup Time        | t <sub>PU</sub>   | From VDD ≥ 1.9 V to ready for a<br>conversion, 25 °C                  | —         | 18   | 25        |      |

|                     |                   | From VDD ≥ 1.9 V to ready for a<br>conversion, full temperature range | —         | _    | 80        | ms   |

|                     |                   | After issuing a software reset command                                | -         | 5    | 15        |      |

Notes:

1. No conversion or I<sup>2</sup>C transaction in progress. Typical values measured at 25 °C.

2. Occurs once during powerup. Duration is <5 msec.

Occurs during I<sup>2</sup>C commands for Reset, Read/Write User Registers, Read EID, and Read Firmware Version. Duration is <100 μs when I<sup>2</sup>C clock speed is >100 kHz (>200 kHz for 2-byte commands).

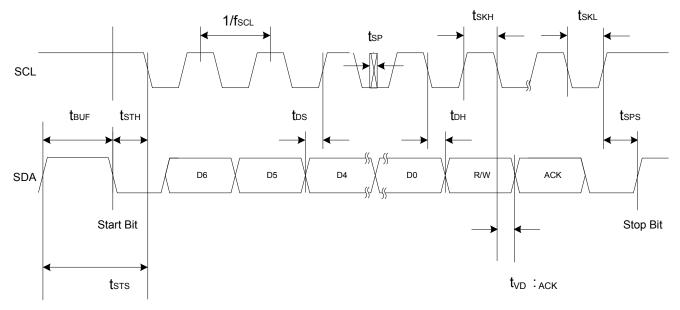

Table 3. I<sup>2</sup>C Interface Specifications<sup>1</sup>  $1.9 \le V_{DD} \le 3.6$  V;  $T_A = -40$  to +125 °C unless otherwise noted.

| Parameter                           | Symbol              | Test Condition                                | Min                    | Тур | Max | Unit |

|-------------------------------------|---------------------|-----------------------------------------------|------------------------|-----|-----|------|

| Hysteresis                          | V <sub>HYS</sub>    | High-to-low versus low-to-<br>high transition | 0.05 x V <sub>DD</sub> | _   | _   | V    |

| SCLK Frequency <sup>2</sup>         | f <sub>SCL</sub>    |                                               |                        |     | 400 | kHz  |

| SCL High Time                       | t <sub>SKH</sub>    |                                               | 0.6                    | _   |     | μs   |

| SCL Low Time                        | t <sub>SKL</sub>    |                                               | 1.3                    | _   | —   | μs   |

| Start Hold Time                     | t <sub>STH</sub>    |                                               | 0.6                    | _   | —   | μs   |

| Start Setup Time                    | t <sub>STS</sub>    |                                               | 0.6                    | _   | —   | μs   |

| Stop Setup Time                     | t <sub>SPS</sub>    |                                               | 0.6                    | _   | —   | μs   |

| Bus Free Time                       | t <sub>BUF</sub>    | Between Stop and Start                        | 1.3                    | _   | —   | μs   |

| SDA Setup Time                      | t <sub>DS</sub>     |                                               | 100                    | _   | —   | ns   |

| SDA Hold Time                       | t <sub>DH</sub>     |                                               | 100                    | —   | —   | ns   |

| SDA Valid Time                      | t <sub>VD;DAT</sub> | From SCL low to data valid                    | —                      | _   | 0.9 | μs   |

| SDA Acknowledge Valid Time          | t <sub>VD;ACK</sub> | From SCL low to data valid                    | —                      | _   | 0.9 | μs   |

| Suppressed Pulse Width <sup>3</sup> | t <sub>SPS</sub>    |                                               | 50                     |     | —   | ns   |

#### Notes:

All values are referenced to V<sub>IL</sub> and/or V<sub>IH</sub>.

Depending on the conversion command, the Si705x may hold the master during the conversion (clock stretch). At above 100 kHz SCL, the Si705x may also hold the master briefly for user register and device ID transactions. At the highest I<sup>2</sup>C speed of 400 kHz the stretching will be <10  $\mu$ s.

3. Pulses up to and including 50 ns will be suppressed.

Figure 1. I<sup>2</sup>C Interface Timing Diagram

#### Table 4. Temperature Sensor

$1.9 \le V_{DD} \le 3.6$  V; TA = -40 to +125 °C default conversion time unless otherwise noted.

| Parameter                  | Symbol           | Test Condition    | Min | Тур   | Max  | Unit   |

|----------------------------|------------------|-------------------|-----|-------|------|--------|

| Operating Range            |                  |                   | -40 | _     | +125 | °C     |

| Accuracy <sup>1</sup>      |                  | Si7053            | _   | ±0.2  | ±0.3 | °C     |

|                            |                  | Si7054            |     | ±0.3  | ±0.4 | °C     |

|                            |                  | Si7055            |     | ±0.4  | ±0.5 | °C     |

|                            |                  | Si7050            | _   | ±0.5  | ±1.0 | °C     |

| Repeatability/Noise        |                  | 14-bit resolution | _   | 0.01  |      |        |

|                            |                  | 13-bit resolution | _   | 0.02  | —    | *O DMO |

|                            |                  | 12-bit resolution | _   | 0.04  |      | °C RMS |

|                            |                  | 11-bit resolution | _   | 0.08  |      | Ť      |

| Response Time <sup>2</sup> | т <sub>63%</sub> | Unmounted device  | _   | 0.7   | —    | S      |

|                            |                  | Si705x-EB board   | _   | 5.1   |      | S      |

| Long Term Stability        |                  |                   | _   | ≤0.01 |      | °C/Yr  |

| Notes:                     |                  |                   |     |       |      |        |

Notes:

1. 14b measurement resolution (default). Values apply to the full operating temperature and voltage range of the device.

2. Time to reach 63% of final value in response to a step change in temperature. Actual response time will vary

dependent on system thermal mass and air-flow.

#### **Table 5. Thermal Characteristics**

| Parameter                            | Symbol          | Test Condition                          | DFN-6 | Unit |

|--------------------------------------|-----------------|-----------------------------------------|-------|------|

| Junction to Air Thermal Resistance   | $\theta_{JA}$   | JEDEC 2-Layer board,<br>No Airflow      | 256   | °C/W |

| Junction to Air Thermal Resistance   | $\theta_{JA}$   | JEDEC 2-Layer board,<br>1 m/s Airflow   | 224   | °C/W |

| Junction to Air Thermal Resistance   | $\theta_{JA}$   | JEDEC 2-Layer board,<br>2.5 m/s Airflow | 205   | °C/W |

| Junction to Case Thermal Resistance  | θ <sub>JC</sub> | JEDEC 2-Layer board                     | 22    | °C/W |

| Junction to Board Thermal Resistance | $\theta_{JB}$   | JEDEC 2-Layer board                     | 134   | °C/W |

### Table 6. Absolute Maximum Ratings<sup>1</sup>

| Parameter                          | Symbol | Test Condition | Min  | Тур | Max       | Unit |

|------------------------------------|--------|----------------|------|-----|-----------|------|

| Ambient temperature<br>under bias  |        |                | -55  | —   | 125       | °C   |

| Storage Temperature <sup>2</sup>   |        |                | -65  |     | 150       | °C   |

| Voltage on I/O pins                |        |                | -0.3 |     | VDD+0.3 V | V    |

| Voltage on VDD with respect to GND |        |                | -0.3 |     | 4.2       | V    |

| ESD Tolerance                      |        | HBM            | _    |     | 2         | kV   |

|                                    |        | CDM            |      |     | 1.25      | kV   |

|                                    |        | MM             | _    |     | 250       | V    |

Notes:

1. Absolute maximum ratings are stress ratings only, operation at or beyond these conditions is not implied and may shorten the life of the device or alter its performance.

2. Special handling considerations apply; see application note, "AN607: Si70xx Humidity and Temperature Sensor Designer's Guide".

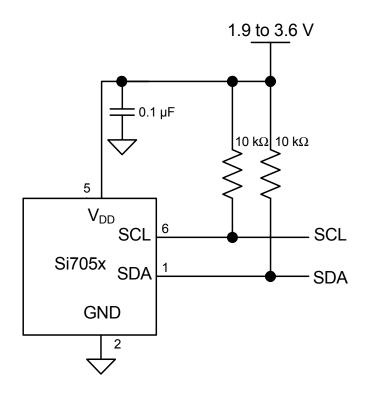

### 2. Typical Application Circuits

Figure 2 demonstrates the typical application circuit for Si705x sensors.

Figure 2. Typical Application Circuit for Temperature Measurement

### 3. Bill of Materials

| Reference | Description                        | Mfr Part Number  | Manufacturer |

|-----------|------------------------------------|------------------|--------------|

| R1        | Resistor, 10 kΩ, ±5%, 1/16 W, 0603 | CR0603-16W-103JT | Venkel       |

| R2        | Resistor, 10 kΩ, ±5%, 1/16 W, 0603 | CR0603-16W-103JT | Venkel       |

| C1        | Capacitor, 0.1 µF, 16 V, X7R, 0603 | C0603X7R160-104M | Venkel       |

| U1        | IC, Digital Temperature Sensor     | Si705x-A20-IM    | Silicon Labs |

### 4. Functional Description

The Si705x Digital Temperature Sensors offer industry-leading low power consumption and high accuracy across the entire operating voltage and temperature range. These monolithic CMOS ICs feature a band-gap temperature sensor element, an analog-to-digital converter with up to 14-bit resolution, signal processing, calibration data, and an I<sup>2</sup>C interface. The patented use of novel signal processing and analog design enables the sensors to maintain their accuracy over a wide temperature and voltage range, while consuming very little current.

The temperature sensors are factory-calibrated and the calibration data is stored in the on-chip non-volatile memory. This ensures that the sensors are fully interchangeable, with no recalibration or software changes required.

The Si705x devices are available in a 3x3 mm DFN package, and the industry-standard I<sup>2</sup>C interface can operate at up to 400 kHz. Requiring just 195nA of average current when sampled once per second, the Si705x can operate for several years with just a single coin cell battery.

The Si705x devices offer an accurate, low-power, factory-calibrated digital solution ideal for measuring temperature in applications ranging from HVAC/R and asset tracking to industrial and consumer platforms.

## 5. I<sup>2</sup>C Interface

The Si705x communicates with the host controller over a digital  $I^2C$  interface. The 7-bit base slave address is 0x40. When sending commands to the device, the R/W bit is set high for a read command and low for a write command.

#### Table 8. I<sup>2</sup>C Slave Address Byte

| A6 | A5 | A4 | A3 | A2 | A1 | A0 | R/W |

|----|----|----|----|----|----|----|-----|

| 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0   |

Master  $I^2C$  devices communicate with the Si705x using a command structure. The commands are listed in the  $I^2C$  command table. Commands other than those documented below are undefined and should not be sent to the device. When sending commands to the device, the R/W bit is set high for a read command and low for a write command.

### Table 9. I<sup>2</sup>C Command Table

| Command Description                      | Command Code |

|------------------------------------------|--------------|

| Measure Temperature, Hold Master Mode    | 0xE3         |

| Measure Temperature, No Hold Master Mode | 0xF3         |

| Reset                                    | 0xFE         |

| Write User Register 1                    | 0xE6         |

| Read User Register 1                     | 0xE7         |

| Read Electronic ID 1st Byte              | 0xFA 0x0F    |

| Read Electronic ID 2nd Byte              | 0xFC 0xC9    |

| Read Firmware Revision                   | 0x84 0xB8    |

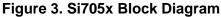

#### 5.1. Issuing a Measurement Command

The measurement command instructs the Si705x to perform a temperature measurement. While the measurement is in progress, the option of either clock stretching (Hold Master Mode) or Not Acknowledging read requests (No Hold Master Mode) is available to indicate to the master that the measurement is in progress; the chosen command code determines which mode is used.

Optionally, a checksum byte can be returned from the slave for use in checking for transmission errors. The checksum byte will follow the least significant measurement byte if it is acknowledged by the master. The checksum byte is not returned if the master "not acknowledges" the least significant measurement byte. The checksum byte is calculated using a CRC generator polynomial of  $x^8 + x^5 + x^4 + 1$ , with an initialization of 0x00.

The checksum byte is optional after initiating a temperature measurement with commands 0xE3, and 0xF3. The checksum byte is required for reading the electronic ID with commands 0xFA 0x0F and 0xFC 0xC9. For all other commands, the checksum byte is not supported.

| Name           | Symbol | Description                                                                                                                                                                                  |

|----------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| START          | S      | SDA goes low while SCL high                                                                                                                                                                  |

| STOP           | Р      | SDA goes high while SCL high                                                                                                                                                                 |

| Repeated START | Sr     | SDA goes low while SCL high. It is allowable to generate a STOP before the repeated start. SDA can transition to high before or after SCL goes high in preparation for generating the START. |

| READ           | R      | Read bit = 0                                                                                                                                                                                 |

| WRITE          | W      | Write bit = 1                                                                                                                                                                                |

| All other bits | —      | SDA value must remain high or low during the entire time SCL is high (this is the set up and hold time in Figure 1)                                                                          |

#### Table 10. I<sup>2</sup>C Bit Descriptions

In the I<sup>2</sup>C sequence diagrams in the following sections, bits produced by the master and slave are color coded as shown:

#### Sequence to perform a measurement and read back result (Hold Master Mode)

| s | Slave<br>Addres |   | W | A     |    | isure<br>nd | A   | Sr    |   | blave<br>ddres |   | R | А | Clock stretch<br>during<br>measurement |

|---|-----------------|---|---|-------|----|-------------|-----|-------|---|----------------|---|---|---|----------------------------------------|

| M | IS Byte         | A |   | LS By | te | NA          | Р   |       |   |                |   |   |   |                                        |

|   |                 |   |   | ·     | >  | А           | Che | cksur | n | NA             | Р |   |   |                                        |

#### Sequence to perform a measurement and read back result (No Hold Master Mode)

#### 5.1.1. Measuring Temperature

The measure temperature commands 0xE3 and 0xF3 will perform a temperature measurement and return the measurement value.

The results of the temperature measurement may be converted to temperature in degrees Celsius (°C) using the following expression:

$Temperature (^{\circ}C) = \frac{175.72*Temp\_Code}{65536} - 46.85$

Where:

Temperature (°C) is the measured temperature value in °C

Temp\_Code is the 16-bit word returned by the Si705x

A temperature measurement will always return XXXXXX00 in the LSB field.

#### 5.2. Reading and Writing User Registers

There is one user register on the Si705x that allows the user to set the configuration of the Si705x. The procedure for accessing that register is described below.

The checksum byte is not supported after reading a user register.

#### Sequence to read a register

| S | Slave<br>Address | W | A | Read Reg<br>Cmd | А | Sr | Slave<br>Address | R | А | Read Data | NA | Ρ |  |

|---|------------------|---|---|-----------------|---|----|------------------|---|---|-----------|----|---|--|

|---|------------------|---|---|-----------------|---|----|------------------|---|---|-----------|----|---|--|

Sequence to write a register

| S Slave Address W A Write Reg Cmd | А | Write Data | А | Р |

|-----------------------------------|---|------------|---|---|

|-----------------------------------|---|------------|---|---|

#### 5.3. Electronic Serial Number

The Si705x provides a serial number individualized for each device that can be read via the I<sup>2</sup>C serial interface.

Two I<sup>2</sup>C commands are required to access the device memory and retrieve the complete serial number. The command sequence, and format of the serial number response is described in the figure below:

| Master | Slave |

|--------|-------|

First access:

| S | Slave Address | W   | АСК | 0xFA | АСК   | 0X0F | АСК |      |   |

|---|---------------|-----|-----|------|-------|------|-----|------|---|

| S | Slave Address | R   | ACK |      |       |      |     |      |   |

|   | SNA_3         | ACK | CRC | ACK  | SNA_2 | АСК  | CRC | ACK  |   |

|   | SNA_1         | ACK | CRC | ACK  | SNA_0 | АСК  | CRC | NACK | Р |

2nd access:

| S | Slave Address | W   | ACK   | 0xFC | ACK | 0XC9 | ACK |

|---|---------------|-----|-------|------|-----|------|-----|

| S | Slave Address | R   | ACK   |      |     |      |     |

|   | SNB_3         | ACK | SNB_2 | АСК  | CRC | ACK  |     |

|   | SNB_1         | ACK | SNB_0 | АСК  | CRC | NACK | Р   |

The format of the complete serial number is 64-bits in length, divided into 8 data bytes. The complete serial number sequence is shown below:

| SNA_3 SNA_2 St | NA_1 SNA_0 SNE | 3_3 SNB_2 S | SNB_1 SNB_0 |

|----------------|----------------|-------------|-------------|

|----------------|----------------|-------------|-------------|

The SNB3 field contains the device identification to distinguish between the different Silicon Labs devices. The value of this field maps to the following devices according to this table:

0x00 or 0xFF engineering samples

50 = 0x32 = Si7050

53 = 0x35 = Si7053

54 = 0x36 = Si7054

55 = 0x37 = Si7055

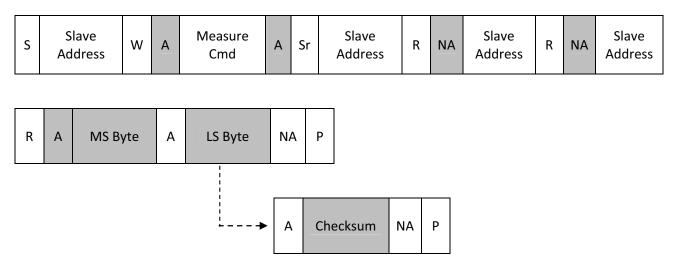

### 5.4. Firmware Revision

The internal firmware revision can be read with the following  $\mathsf{I}^2\mathsf{C}$  transaction:

The values in this field are encoded as follows:

0xFF = Firmware version 1.0

0x20 = Firmware version 2.0

### 6. Control Registers

| Register        | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-----------------|-------|-------|-------|-------|-------|-------|-------|-------|

| User Register 1 | RES1  | VDDS  | RSVD  | RSVD  | RSVD  | RSVD  | RSVD  | RES0  |

Table 11. Register Summary

Notes:

1. Any register not listed here is reserved and must not be written. The result of a read operation on these bits is undefined.

2. Except where noted, reserved register bits will always read back as "1," and are not affected by write operations. For future compatibility, it is recommended that prior to a write operation, registers should be read. Then the values read from the RSVD bits should be written back unchanged during the write operation.

#### 6.1. Register Descriptions

#### **Register 1. User Register 1**

| Bit  | D7   | D6   | D5   | D4   | D3   | D2   | D1   | D0   |

|------|------|------|------|------|------|------|------|------|

| Name | RES1 | VDDS | RSVD | RSVD | RSVD | RSVD | RSVD | RES0 |

| Туре | R/W  | R    | R/W  | R/   | W    | R/W  | R/W  | R/W  |

Reset Settings = 0011\_1010

| Bit                   | Name     | Function                                                                                                                                                                                                                                                                                                                  |

|-----------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D7; D0                | RES[1:0] | Measurement Resolution:                                                                                                                                                                                                                                                                                                   |

|                       |          | 00:       14 bit         01:       12 bit         10:       13 bit         11:       11 bit                                                                                                                                                                                                                               |

| D6                    | VDDS     | VDD Status:         0:       V <sub>DD</sub> OK         1:       V <sub>DD</sub> Low         The minimum recommended operating voltage is 1.9 V. A transition of the VDD status bit from 0 to 1 indicates that VDD is between 1.8 V and 1.9 V. If the VDD drops below 1.8 V, the device will no longer operate correctly. |

| D5, D4, D3,<br>D2, D1 | RSVD     | Reserved                                                                                                                                                                                                                                                                                                                  |

## Si7050/3/4/5-A20

## 7. Pin Descriptions: Si705x (Top View)

| Pin Name         | Pin #  | Pin Description                                                                                                                                                     |

|------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SDA              | 1      | I <sup>2</sup> C data                                                                                                                                               |

| GND              | 2      | Ground. This pin is connected to ground on the circuit board through a trace. Do not connect directly to GND plane.                                                 |

| VDD              | 5      | Power. This pin is connected to power on the circuit board.                                                                                                         |

| SCL              | 6      | I <sup>2</sup> C clock                                                                                                                                              |

| DNC              | 3,4    | These pins should be soldered to pads on the PCB for mechanical stability; they can be electrically floating or tied to VDD (do not tie to GND).                    |

| T <sub>GND</sub> | Paddle | This pad is connected to GND internally. This pad is the main thermal input to the on-<br>chip temperature sensor. The paddle should be soldered to a floating pad. |

### 8. Ordering Guide

| Part Number           | Description                                       | Max. Accuracy | Pkg   | Packing Format |

|-----------------------|---------------------------------------------------|---------------|-------|----------------|

| Si7050-A20-IM         | Digital temperature sensor                        | ±1 °C         | DFN 6 | Tube           |

| Si7050-A20-IMR        | Digital temperature sensor                        | ±1 °C         | DFN 6 | Tape and Reel  |

| Si7050-A20-YM0        | Digital temperature sensor — Automotive           | ±1 °C         | DFN 6 | Tube           |

| Si7050-A20-YM0R       | Digital temperature sensor — Automotive           | ±1 °C         | DFN 6 | Tape and Reel  |

| Si7053-A20-IM         | Digital temperature sensor                        | ±0.3 °C       | DFN 6 | Tube           |

| Si7053-A20-IMR        | Digital temperature sensor                        | ±0.3 °C       | DFN 6 | Tape and Reel  |

| Si7053-A20-YM0        | Digital temperature sensor — Automotive           | ±0.3 °C       | DFN 6 | Tube           |

| Si7053-A20-YM0R       | Digital temperature sensor — Automotive           | ±0.3 °C       | DFN 6 | Tape and Reel  |

| Si7054-A20-IM         | Digital temperature sensor                        | ±0.4 °C       | DFN 6 | Tube           |

| Si7054-A20-IMR        | Digital temperature sensor                        | ±0.4 °C       | DFN 6 | Tape and Reel  |

| Si7054-A20-YM0        | Digital temperature sensor — Automotive           | ±0.4 °C       | DFN 6 | Tube           |

| Si7054-A20-YM0R       | Digital temperature sensor — Automotive           | ±0.4 °C       | DFN 6 | Tape and Reel  |

| Si7055-A20-IM         | Digital temperature sensor                        | ±0.5 °C       | DFN 6 | Tube           |

| Si7055-A20-IMR        | Digital temperature sensor                        | ±0.5 °C       | DFN 6 | Tape and Reel  |

| Si7055-A20-YM0        | Digital temperature sensor — Automotive           | ±0.5 °C       | DFN 6 | Tube           |

| Si7055-A20-YM0R       | Digital temperature sensor — Automotive           | ±0.5 °C       | DFN 6 | Tape and Reel  |

| Note: The "A" denotes | product revision A and "20" denotes firmware vers | ion 2.0.      | ·     |                |

### Table 12. Device Ordering Guide

### 9. Package Outline

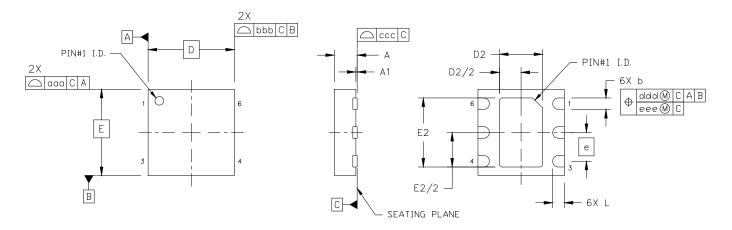

### 9.1. Package Outline: 3x3 6-pin DFN

Figure 10. 3x3 6-pin DFN

| Dimension | Min       | Nom  | Max  |  |

|-----------|-----------|------|------|--|

| Α         | 0.65      | 0.75 | 0.85 |  |

| A1        | 0.00      | 0.02 | 0.05 |  |

| A3        | 0.203 REF |      |      |  |

| b         | 0.35      | 0.40 | 0.45 |  |

| D         | 3.00 BSC. |      |      |  |

| е         | 1.00 BSC. |      |      |  |

| E         | 3.00 BSC. |      |      |  |

| D2        | 2.30      | 2.40 | 2.50 |  |

| E2        | 1.4       | 1.5  | 1.6  |  |

| К         | 0.20 MIN. |      |      |  |

| L         | 0.35      | 0.40 | 0.45 |  |

| Ν         | 6         |      |      |  |

| ND        | 3         |      |      |  |

Table 13. 3x3 6-pin DFN Package Diagram Dimensions

1. All dimensions shown are in millimeters (mm).

2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

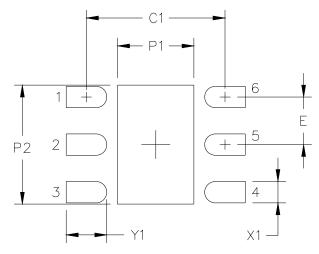

### 10. PCB Land Pattern and Solder Mask Design

Figure 4. Si705x PCB Land Pattern

| Table 14 | PCB | Land | Pattern | Dimensions |

|----------|-----|------|---------|------------|

|----------|-----|------|---------|------------|

| Symbol | mm   |

|--------|------|

| C1     | 2.90 |

| E      | 1.00 |

| P1     | 1.60 |

| P2     | 2.50 |

| X1     | 0.45 |

| Y1     | 0.85 |

### Notes:

- General

- 1. All dimensions shown are at Maximum Material Condition (MMC). Least Material Condition (LMC) is calculated based on a Fabrication Allowance of 0.05 mm.

- 2. This Land Pattern Design is based on the IPC-7351 guidelines.

#### Solder Mask Design

3. All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be  $60 \ \mu m$  minimum, all the way around the pad.

#### Stencil Design

- **4.** A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

- 5. The stencil thickness should be 0.125 mm (5 mils).

- 6. The ratio of stencil aperture to land pad size should be 1:1 for all perimeter pins.

- **7.** A 2x1 array of 1.00 mm square openings on 1.30 mm pitch should be used for the center ground pad to achieve a target solder coverage of 50%.

#### Card Assembly

- **8.** A No-Clean, Type-3 solder paste is recommended.

- **9.** The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

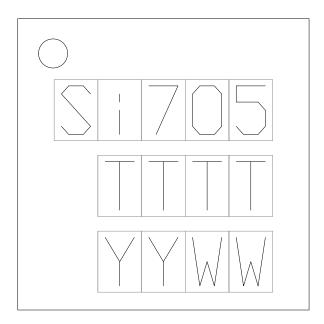

### 11. Top Marking

### 11.1. Si705x Top Marking

### **11.2. Top Marking Explanation**

| Mark Method:        | Laser                                             |                                                                                                      |

|---------------------|---------------------------------------------------|------------------------------------------------------------------------------------------------------|

| Pin 1 Mark:         | Circle = 0.30 mm Diameter (Upper-<br>Left Corner) |                                                                                                      |

| Font Size:          | 0.05 mm                                           |                                                                                                      |

| Line 1 Mark Format: | Device Code                                       | Si7005                                                                                               |

| Line 2 Mark Format: | ТТТТ                                              | Manufacturing Code from the<br>Assembly Purchase Order form.                                         |

| Line 3 Mark Format: | YY = Year<br>WW = Work Week                       | Assigned by the Assembly House.<br>Corresponds to the year and work<br>week of the assembly release. |

### 12. Additional Reference Resources

• AN607: Si70xx Humidity and Temperature Sensor Designer's Guide

### **DOCUMENT CHANGE LIST**

### Revision 0.9 to Revision 1.0

- Updated Section "5. I2C Interface" on page 12

- Updated Table 12, "Device Ordering Guide," on page 19

### **CONTACT INFORMATION**

Silicon Laboratories Inc. 400 West Cesar Chavez Austin, TX 78701 Tel: 1+(512) 416-8500 Fax: 1+(512) 416-9669

Toll Free: 1+(877) 444-3032 Please visit the Silicon Labs Technical Support web page: http://www.siliconlabs.com/support/pages/contacttechnicalsupport.aspx and register to submit a technical support request.

#### **Patent Notice**

Silicon Labs invests in research and development to help our customers differentiate in the market with innovative low-power, small size, analogintensive mixed-signal solutions. Silicon Labs' extensive patent portfolio is a testament to our unique approach and world-class engineering team.

The information in this document is believed to be accurate in all respects at the time of publication but is subject to change without notice. Silicon Laboratories assumes no responsibility for errors and omissions, and disclaims responsibility for any consequences resulting from the use of information included herein. Additionally, Silicon Laboratories assumes no responsibility for the functioning of undescribed features or parameters. Silicon Laboratories reserves the right to make changes without further notice. Silicon Laboratories makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Silicon Laboratories assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. Silicon Laboratories products are not designed, intended, or authorized for use in applications intended to support or sustain life, or for any other application in which the failure of the Silicon Laboratories product could create a situation where personal injury or death may occur. Should Buyer purchase or use Silicon Laboratories products for any such unintended or unauthorized application, Buyer shall indemnify and hold Silicon Laboratories harmless against all claims and damages.

Silicon Laboratories and Silicon Labs are trademarks of Silicon Laboratories Inc. Other products or brandnames mentioned herein are trademarks or registered trademarks of their respective holders.